# DESIGN OF ISOLATED DC-DC AND DC-DC-AC CONVERTERS WITH REDUCED NUMBER OF POWER SWITCHES

A Thesis

Submitted to the Faculty

of

Purdue University

by

Dhara I. Mallik

In Partial Fulfillment of the

Requirements for the Degree

of

Master of Science in Electrical and Computer Engineering

August 2017

Purdue University

Indianapolis, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

Dr. Euzeli Cipriano dos Santos, Chair

Department of Electrical and Computer Engineering

Dr. Mohamed El-Sharkawy

Department of Electrical and Computer Engineering

Dr. Maher Rizkalla

Department of Electrical and Computer Engineering

# Approved by:

Dr. Brian King

Head of the Graduate Program

Dedicated to my beloved parents

Munmun Manabee and Dr. M S I Mullick

Ma ♥ Bapi

#### **ACKNOWLEDGMENTS**

I would like to thank my thesis supervisor and mentor Dr. Euzeli C. dos Santos, for his guidance and inspiration through the research process and course-works. I am grateful to all my committee members.

I am immensely indebted to Dr. Brian King, the Head of the Department, not only for his guidance since the very first year of my graduate studies but also for being a continuous support.

I am grateful to the other faculty members and staff. I would especially like to mention Sherrie for keep enduring my constant nudging always with a welcoming smile. I want to thank my lab-mates for their support whenever I asked and even when I did not ask.

I owe everything to my loving parents who kept sacrificing for me since the day I was born. Even being a thousand of miles away, they never stopped encouraging, motivating and telling me to dream bigger. I am also grateful to my other family members for keeping me going. Finally, I would like to thank Ragib, for having the courage to hold my hands even during the most struggling and uncertain times.

# TABLE OF CONTENTS

|    |                |                          |                                     | Page  |  |  |  |  |

|----|----------------|--------------------------|-------------------------------------|-------|--|--|--|--|

| LI | LIST OF TABLES |                          |                                     |       |  |  |  |  |

| LI | ST OI          | FIGUE                    | RES                                 | . ix  |  |  |  |  |

| SY | MBC            | DLS                      |                                     | . xii |  |  |  |  |

| Αŀ | ABBREVIATIONS  |                          |                                     |       |  |  |  |  |

| Αŀ | ABSTRACT       |                          |                                     |       |  |  |  |  |

| 1  | INTI           | RODUC                    | TION                                | . 1   |  |  |  |  |

|    | 1.1            | Power                    | Processing                          | . 1   |  |  |  |  |

|    | 1.2            | Dc-dc                    | Converter                           | . 3   |  |  |  |  |

|    |                | 1.2.1                    | Isolated dc-dc Converter            | . 4   |  |  |  |  |

|    | 1.3            | Dc-ac                    | Converter                           | . 4   |  |  |  |  |

|    | 1.4            | Multip                   | le Output Converters                | . 5   |  |  |  |  |

| 2  | CON            | IVENTI                   | ONAL CONFIGURATIONS                 | . 6   |  |  |  |  |

|    | 2.1            | Introdu                  | action                              | . 6   |  |  |  |  |

|    | 2.2            | Single                   | Input Single Output Dc-dc Converter | . 6   |  |  |  |  |

|    |                | 2.2.1                    | Converter Configuration             | . 6   |  |  |  |  |

|    |                | 2.2.2                    | Transfer Function                   | . 7   |  |  |  |  |

|    |                | 2.2.3                    | Switching Signals                   | . 7   |  |  |  |  |

|    |                | 2.2.4                    | Generation Gating Signals           | . 8   |  |  |  |  |

|    | 2.3            | Single                   | Input Dual Output Dc-dc Converter   | . 12  |  |  |  |  |

|    |                | 2.3.1                    | Converter Configuration             | . 13  |  |  |  |  |

|    |                | 2.3.2                    | Gating Signal Circuitry             | . 13  |  |  |  |  |

|    |                | 2.3.3                    | Transfer Function                   | . 14  |  |  |  |  |

|    | 2.4            | Dc-Ac                    | Converter                           | . 15  |  |  |  |  |

| 3  | PRO            | POSED DC-DC CONVERTER 19 |                                     |       |  |  |  |  |

|   |      | Pag                                                   | ge |

|---|------|-------------------------------------------------------|----|

|   | 3.1  | Introduction                                          | 19 |

|   | 3.2  | Motivation                                            | 19 |

|   | 3.3  | Design Requirements                                   | 21 |

|   | 3.4  | Converter Design and Layout                           | 22 |

|   | 3.5  | Switching States                                      | 22 |

|   | 3.6  | Gating Signals                                        | 25 |

|   |      | 3.6.1 Serially Connected Loads Operate Together       | 26 |

|   |      | 3.6.2 Serially Connected Loads Operate Separately     | 26 |

|   |      | 3.6.3 Parallel Connection of the Load                 | 30 |

|   | 3.7  | Selection of Gating Signal for the Proposed Converter | 30 |

|   | 3.8  | Switching State Diagrams                              | 34 |

|   | 3.9  | Switching Signal Circuitry                            | 37 |

|   | 3.10 | Steady State Analysis                                 | 41 |

|   | 3.11 | Feedback Control System                               | 43 |

| 4 | RESU | ULTS OBTAINED FROM THE PROPOSED DC-DC CONVERTER 4     | 46 |

|   | 4.1  | Introduction                                          | 46 |

|   | 4.2  | Circuit Diagrams to Simulate Proposed Dc-dc Converter | 46 |

|   | 4.3  | Results From Simulation                               | 49 |

|   | 4.4  | Calculations                                          | 50 |

|   | 4.5  | Special Condition                                     | 52 |

|   | 4.6  | Comparison with The Conventional Converter            | 54 |

|   |      | 4.6.1 Generation of Output Voltage                    | 54 |

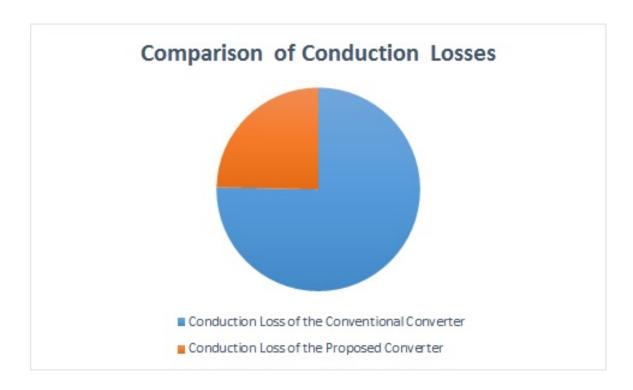

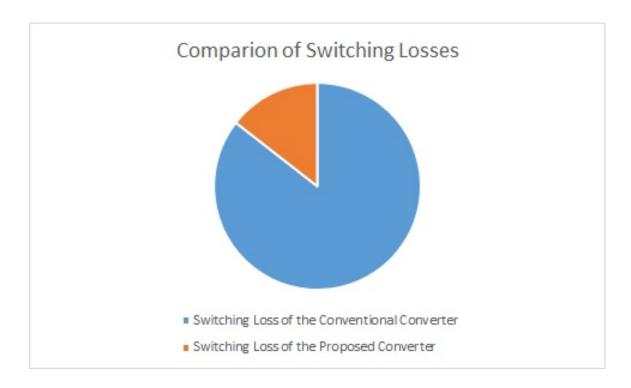

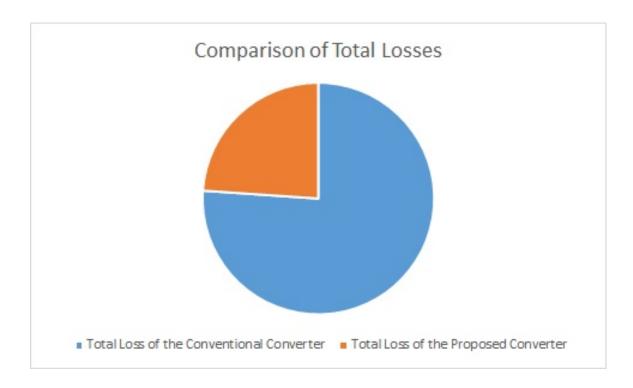

|   |      | 4.6.2 Power Loss                                      | 55 |

|   |      | 4.6.3 Number of Components Required                   | 66 |

| 5 | PROI | POSED DC-DC-AC CONVERTER                              | 67 |

|   | 5.1  | Introduction                                          | 67 |

|   | 5.2  | Motivation                                            | 68 |

|   | 5.3  | Design Layout                                         | 68 |

|    |       |        |                                             | Page |

|----|-------|--------|---------------------------------------------|------|

|    |       | 5.3.1  | Dc-dc Converter                             | . 69 |

|    |       | 5.3.2  | Dc-ac Converter                             | . 70 |

|    | 5.4   | Three  | Phase Voltage Source Inverters              | . 70 |

|    | 5.5   | Conve  | rter Layout                                 | . 71 |

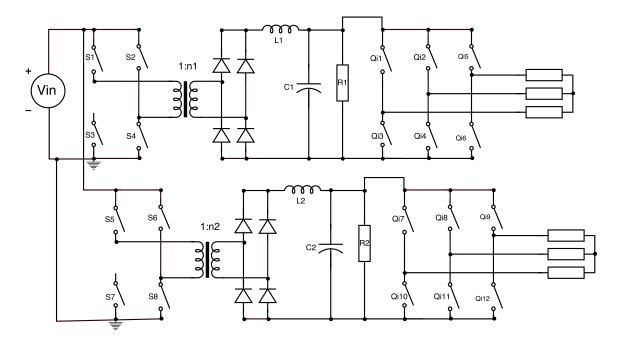

|    |       | 5.5.1  | Dual Output Converter with Eight Switches   | . 71 |

|    |       | 5.5.2  | Dual Output Converter with Six Switches     | . 72 |

|    |       | 5.5.3  | Dual Output Converter with Fault Correction | . 72 |

|    | 5.6   | Gating | g Signal                                    | . 73 |

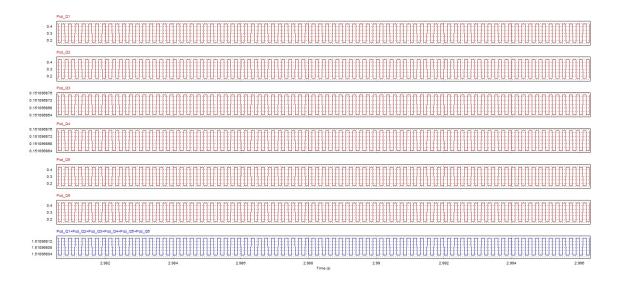

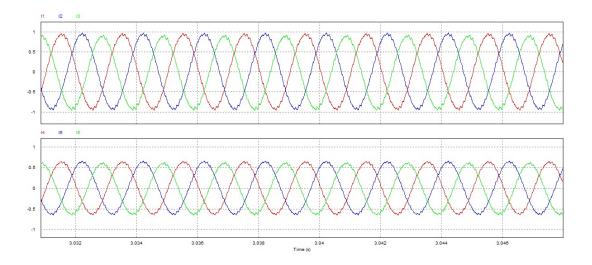

| 6  | RES   | ULTS F | FROM DESIGNED DC-DC-AC CONVERTER            | . 76 |

|    | 6.1   | Introd | uction                                      | . 76 |

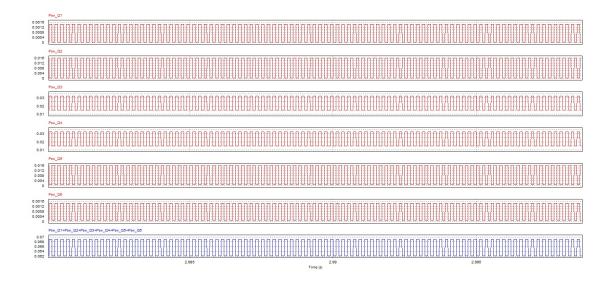

|    | 6.2   | Gating | g Signals                                   | . 76 |

|    | 6.3   | Single | e Input Dual Output Dc-ac Converter         | . 79 |

| 7  | CON   | ICLUSI | ON                                          | . 82 |

|    | 7.1   | Discus | ssions on the Designed Converters           | . 82 |

|    |       | 7.1.1  | Single Input Dual Output Dc to Dc Converter | . 82 |

|    |       | 7.1.2  | Single Input Dual Output Dc to Ac Converter | . 82 |

|    | 7.2   | Sugge  | sted Improvements                           | . 82 |

| RI | FFFRI | FNCES  |                                             | 84   |

# LIST OF TABLES

| Tabl | e                                                                                 | Pag | ţе |

|------|-----------------------------------------------------------------------------------|-----|----|

| 2.1  | All Possible States of the Four Switches                                          |     | 8  |

| 2.2  | States Considered to Generate the Gating Signals                                  |     | 9  |

| 2.3  | Generating the Four Required Signals                                              |     | 9  |

| 3.1  | All topological states                                                            | . 2 | .3 |

| 3.2  | States Considered to Generate the Gating Signals                                  | . 2 | .7 |

| 3.3  | Logic Table to Generate the Gating Signals                                        | . 2 | .7 |

| 3.4  | Desired Switching States                                                          | . 3 | 2  |

| 3.5  | Generation of the Switching Signals for the Switches Q1 and Q2                    | . 3 | 2  |

| 3.6  | Generation of the Switching Signals for the Switch Q3 (Initial)                   | . 3 | 3  |

| 3.7  | Generation of the Switching Signals for the Switch Q3 (Final)                     | . 3 | 4  |

| 3.8  | Generation of the Switching Signals for the Switch Q4                             | . 3 | 5  |

| 4.1  | Parameters of Simulation Control                                                  | . 4 | .9 |

| 4.2  | Output Voltage of Conventional and Proposed Converter with Changing Input Voltage | . 5 | 4  |

| 6.1  | Parameters Included for the Triangular Wave                                       | . 7 | 6  |

| 6.2  | Parameters Included for the Sine Waves                                            | . 7 | 7  |

# LIST OF FIGURES

| Figu | re                                                              | Page |

|------|-----------------------------------------------------------------|------|

| 1.1  | Electric Power Conversion System                                | . 1  |

| 1.2  | Converter Power Loss vs. Efficiency                             | . 3  |

| 2.1  | Full-bridge Single Input Single Output Dc-dc Converter          | . 6  |

| 2.2  | Logic Circuit to Generate Switching Signals                     | . 10 |

| 2.3  | Generation of Sig1 from a Triangular Wave and a Dc Voltage      | . 11 |

| 2.4  | Generation of Sig2 from a Triangular Wave and a Dc Voltage      | . 11 |

| 2.5  | Generation of Q1 from Sig1 and Sig2                             | . 12 |

| 2.6  | Generation of Q2 from Sig1' and Sig2'                           | . 13 |

| 2.7  | Full-bridge Single Input Dual Output Dc-dc Converter            | . 14 |

| 2.8  | Logic Circuit to Generate Switching Signals                     | . 15 |

| 2.9  | Conventional Single-Input Single-output Inverter                | . 16 |

| 2.10 | Single-input Dual-output Dc-dc-ac Converter with Eight Switches | . 16 |

| 2.11 | Switching Signal Generation of Dc-ac Converter                  | . 17 |

| 3.1  | Proposed Single Input Dual Output Dc-dc Converter               | . 22 |

| 3.2  | Primary Side Voltages of the Loads for Series Connection        | . 28 |

| 3.3  | Primary Side Voltages with Increased Duty Cycle for Load-1      | . 29 |

| 3.4  | Primary Side Voltages of the Loads for Parallel Connection      | . 31 |

| 3.5  | Equivalent Circuit for the First State                          | . 36 |

| 3.6  | Equivalent Circuit for the Second State                         | . 37 |

| 3.7  | Equivalent Circuit for the Third State                          | . 38 |

| 3.8  | Equivalent Circuit for the Fourth State                         | . 39 |

| 3.9  | All Six Switching Signals                                       | . 40 |

| 3.10 | Circuitry to Generate Gating Signals                            | . 41 |

| 3.11 | Inductor Voltages and Currents for Output1 and Output2          | . 42 |

| Figu | re                                                                                                     | age |

|------|--------------------------------------------------------------------------------------------------------|-----|

| 3.12 | Basic Feedback Control System for the Converter                                                        | 44  |

| 3.13 | Feedback Control System for the Converter                                                              | 44  |

| 4.1  | Diagram in PSIM to Simulate the Designed Converter                                                     | 47  |

| 4.2  | Gating Circuitry to Generate the Switching Signals                                                     | 48  |

| 4.3  | Four Switching Signals Generated to Control the Voltage at Primary Side                                | 50  |

| 4.4  | Primary Side Voltages [Upper one with 0.8 duty cycle and lower one with 0.5 duty cycle]                | 51  |

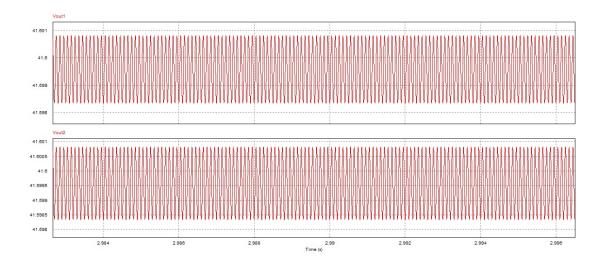

| 4.5  | Output Voltages of Load-1 and Load-2                                                                   | 51  |

| 4.6  | Primary Side Voltages [Upper one with 0.5 duty cycle and lower one with 0.8 duty cycle]                | 53  |

| 4.7  | Output Voltages of Load-1 and Load-2 [Upper one with 0.5 duty cycle and lower one with 0.8 duty cycle] | 53  |

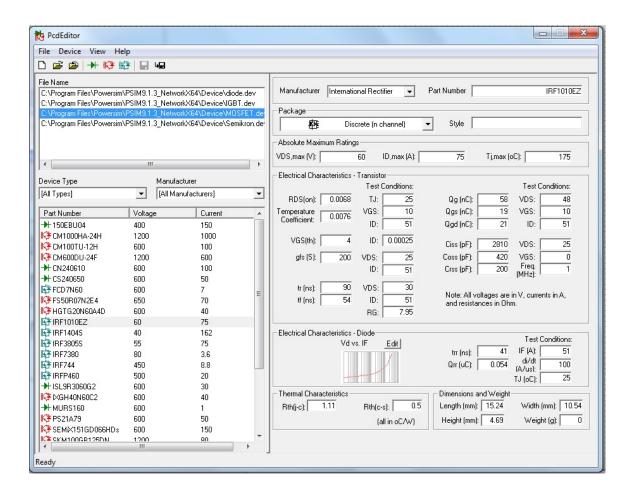

| 4.8  | MOSFET Properties in the PcdEditor Window in PSIM                                                      | 56  |

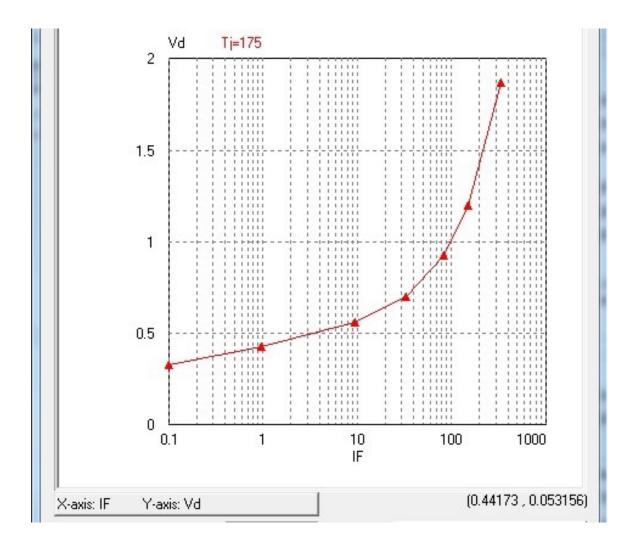

| 4.9  | Diode Voltage Drop vs Diode Forward Current of the Switch                                              | 57  |

| 4.10 | Diagram to Calculate the Losses in Conventional Configuration                                          | 58  |

| 4.11 | Diagram to Calculate the Losses in Conventional Configuration                                          | 58  |

| 4.12 | Conduction Losses of the Switches in the Conventional Configuration                                    | 59  |

| 4.13 | Conduction Losses of the Switches in the Proposed Design                                               | 60  |

| 4.14 | Comparison Between the Conduction Losses of the Conventional and Proposed Configuration                | 61  |

| 4.15 | Switching Losses of the Switches in the Conventional Configuration                                     | 62  |

| 4.16 | Switching Losses of the Switches in the Proposed Design                                                | 63  |

| 4.17 | Comparison Between the Switching Losses of the Conventional and Proposed Configuration                 | 64  |

| 4.18 | Total Loss in the Conventional Configuration                                                           | 65  |

| 4.19 | Total Loss in the Proposed Design                                                                      | 65  |

| 4.20 | Comparison Between the Total Losses of the Conventional and Proposed Configuration                     | 66  |

| 5.1  | The Planned Layout of the Converter                                                                    | 69  |

| 5.2  | Triangular Wave and Three Sine Waves to Generate Switching Signals                                     | 71  |

| Figu | re                                                    | Pa | ıge |

|------|-------------------------------------------------------|----|-----|

| 5.3  | Single-input Dual-output Inverter with Eight Switches |    | 72  |

| 5.4  | Single-input Dual-output Inverter with Six Switches   |    | 73  |

| 5.5  | Open-end Winding System                               |    | 74  |

| 5.6  | Switching Signal Generation of Dc-ac Converter        |    | 75  |

| 6.1  | Gating Signal Generation Circuitry                    |    | 78  |

| 6.2  | Waves to Generate Switching Signals                   |    | 78  |

| 6.3  | Generated Switching Signals for Six Switches          |    | 79  |

| 6.4  | Circuit Diagram for the Proposed Design               |    | 80  |

| 6.5  | Output Currents                                       |    | 80  |

| 6.6  | Line to Line Voltages                                 |    | 81  |

# **SYMBOLS**

- m mass

- V voltage

- I current

- P power

- $\eta$  turns ratio

- D duty cycle

- $^{\circ}C$  degree Celsius

- & AND gate

- OR gate

- $\overline{x}$  NOT gate(NOT x)

- → XOR gate

## **ABBREVIATIONS**

SISO single input single output

SIDO single input dual output

PWM pulse width modulation

dc direct current

ac alternating current

Op-Amp operational amplifier

RoHS restriction of hazardous substances

### **ABSTRACT**

Mallik, Dhara I. M.S.E.C.E., Purdue University, August 2017. Design of Isolated Dc-dc and Dc-dc-ac Converters with Reduced Number of Power Switches. Major Professor: Euzeli C. dos Santos.

There are various types of power electronic converters available in recent days. In some applications (e.g. PC power supply), it is required to supply more than one load from a single power supply. One of the main challenges while designing a power converter is to increase its efficiency especially when the number of power switches employed is relatively large. While several loads are supplied from a single source, if the power loss in the switches cannot be reduced, then the expected utilization of using a single source is not very feasible. To reduce the loss and increase efficiency, the thesis presents a novel design with reduced number of switches.

The scope of this thesis is not limited to the dc-dc converter only, the converter to supply three phase ac loads from a single dc source is also presented. This discussion includes an improved fault tolerant configuration of the inverter part. The generated waveforms from the simulations are included as a demonstration of satisfactory results.

### 1. INTRODUCTION

Since the time of ancient Greek through the discovery of electricity by Benjamin Franklin, electricity has been an inseparable part of human life. Communication, entertainment, mechanical work, light, computing and all tangible benefits of energy and electricity cannot be denied. The enormous involvement of electricity requires control and conversion to meet modern day requirements. From the need to control the flow of electricity to manage the conversion of energy the area of Power Electronics was introduced [1].

## 1.1 Power Processing

Since the invention of mercury arc rectifier in 1902 to convert alternating current to direct current [2] [3], the revolutionary era of power electronic devices had been started. Application of mercury arc valves in power grids, the high-vacuum and gas-filled diode thermionic rectifiers, triggered devices such as the thyratron and ignitron were being widely used. In the beginning, power electronics [4], [5], [6], [7] mainly focused on advancing devices that provide the capability to handle high power levels. Then the focus transitioned to the application of the semiconductor devices [8] with suitable power rating to meet broader requirements of novel products. Recently it was expanded to multidisciplinary technology such as artificial intelligence and neural network [9].

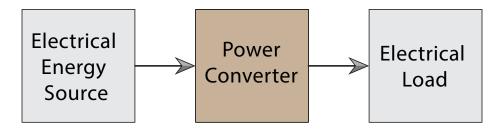

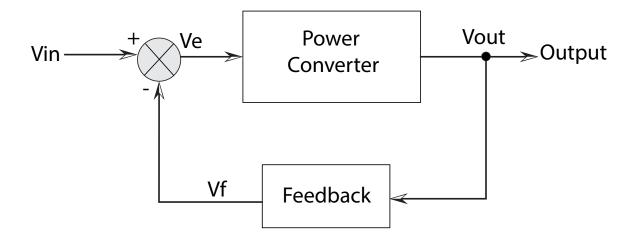

Fig. 1.1. Electric Power Conversion System

To meet the user requirements, a systematic method was developed in [10] to link technical power packaging issues. The framework explores the general power conversion system as depicted in figure 1.1. The input power is processed by the converter as specified and yield to the conditioned output power to supply to the load.

In power processing applications, efficiency is a crucial factor. Construction of low efficiency converters producing substantial output power does not simply meet the practical necessity [11]. If *Pout* is the output power and *Pin* is the input power then efficiency  $\eta$  is,

$$\eta = \frac{Pout}{Pin} \tag{1.1}$$

During the conversion process the lost power is the difference between the input and output power. The lost power *Ploss* is,

$$Ploss = Pin - Pout (1.2)$$

$$= \frac{Pout}{\eta} - Pout \tag{1.3}$$

$$= Pout(\frac{1}{\eta} - 1) \tag{1.4}$$

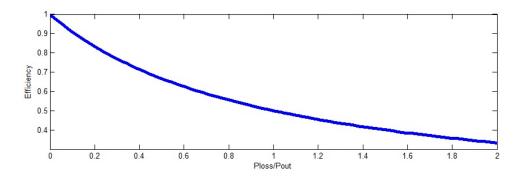

From equation (1.3), if the efficiency is needed to be plotted, then,

$$\frac{Ploss}{Pout} = \frac{1}{n} - 1 \tag{1.5}$$

The equation (1.5) is plotted in Matlab to generate the graph to depict the ratio of power loss to output power vs. the efficiency of the converter.

Figure 1.2 shows the plotted data. According to [11], if the converter has an efficiency of 50 percent, then the loss during the conversion is equal to the output power. This energy is converted to heat which needs to be removed from the converter. Therefore a large and expensive cooling process is required for the system. So only increasing the efficiency can lead to reducing the expense and producing higher output. So much effort is given in the converter design process to improve the efficiency.

The power electronic conversion process can be one of four types:

#### 1. Alternating current (AC) to direct current(DC)

Fig. 1.2. Converter Power Loss vs. Efficiency

- 2. Direct current (DC) to alternating current(DC)

- 3. Direct current (DC) to direct current(DC)

- 4. Alternating current (AC) to alternating current(DC)

In this thesis, the dc to dc conversion and then dc to ac conversion were taken into consideration.

#### 1.2 Dc-dc Converter

Since the 1940's, the growth of dc-dc converters has increased due to the high demand of dc-dc converter in industrial applications, computer hardware circuitry and trend in high power and high voltage density related applications [12]. Switching mode dc-dc converters are more efficient than linear converters as the transistors operate as switches and dissipate less power. PWM dc-dc converters are capable of conducting in step-up, step-down mode and can have multiple output voltages whereas linear regulators can operate only as step-down converters [13]. High step-up converters are especially required in the wide range of applications of energy sources like photo-voltaic panels and fuel cells which have variable input voltage range and low output voltage [14], [15]. In the systems where the generated power is needed to transmit to a long distance like offshore wind power [16], high-voltage

direct current (HVDC) transmission systems have lower cable loss than high-voltage alternating current (HVAC) transmission systems [17]. HVDC technology is considered as the main element of multi-terminal grid [18].

#### 1.2.1 Isolated dc-dc Converter

As discussed above,in HVDC transmission systems, the regulation of voltage is very important and for that reason a stable control system is needed for the dc-dc converter. In [19], PWM based adaptive sliding mode control was presented for boost converter. An interleaved converter with voltage multiplier was proposed in [20] that has reduced switching loss but this kind of converter lacks proper control system in applications other than electric vehicles. Cascode technique along with inductor coupling was implemented for high step-up operation in [21]. But over these traditional converters, isolated dc-dc converters have many advantages in electrical isolation, high reliability, ease of realizing softswitching control and bidirectional energy flow [22]. Another investigation [23] showed that three-level full bridge dc-dc converters are capable of improving light load efficiency compared to two-level dc-dc converters as the switches are exposed to lesser dc voltage.

Therefore, in this work, while designing converter, full bridge isolated type was considered.

#### 1.3 Dc-ac Converter

Dc to ac converter is called the power inverter which converts direct current to alternating current. From the 1970's different prototypes of dc to ac conversion process started to formed for various uses such as supply a low-pressure mercury vapor discharge pump [24], then later transformer [25], [26] were utilized.

## 1.4 Multiple Output Converters

Dc-dc converter with single output is insufficient in many applications. For doubly fed machines like electric tractor locomotives or elevators are required to operate from one input source [27]. Multiple outputs with wide range applications in hybrid electric vehicles [28], LED lighting [29], dc based nano-grids [30], stand-by power supplies etc. [31], [32]. In addition, the setup where two loads can be operated from the same source reduce the bulkiness of the conventional converters and provide more compactness, cost effectiveness [33] and have higher efficiency [34]. Single input dual output buck converters were also explored for both unidirectional and bidirectional operations and utilization of power switches [35], [36]. Similar characteristics in reducing power loss and improving efficiency in full-bridge isolated dc-dc converter was explored in this thesis.

Many applications require ac output voltage that matches the frequency of the grid. Novel inverters are discovered day by day as they have broad applications like induction heating cooking appliances [37], inverter based microgrid system [38], hybrid multilevel conversion [39] and so on. Hybrid inverter is used in high voltage heating, ventilation and air conditioning system [40]. In such applications especially where the load is supplied from two separate dc-ac converters, the use of single input to dual ac output can be very cost effective. In this thesis, a dual ac output from a single dc input was investigated and proposed.

# 2. CONVENTIONAL CONFIGURATIONS

### 2.1 Introduction

A bidirectional isolated dc-dc converter was proposed in [41] for operation in medium voltage range. This type of galvanic isolation of the converters are suitable for energy storage system [42]. According to [43], when full-bridge switching circuit is used, the input and output voltage are significantly proportionate. For distributed power generation in residential systems, isolated dc-dc step up converters can be utilized [44].

## 2.2 Single Input Single Output Dc-dc Converter

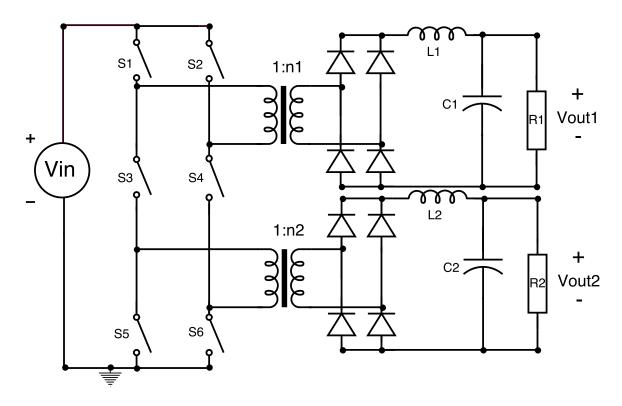

## 2.2.1 Converter Configuration

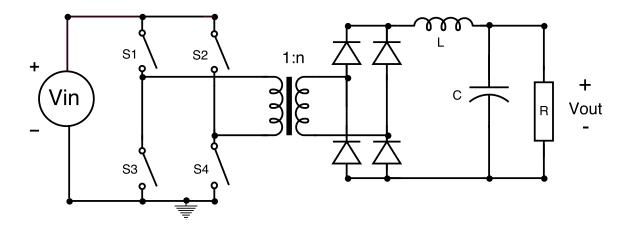

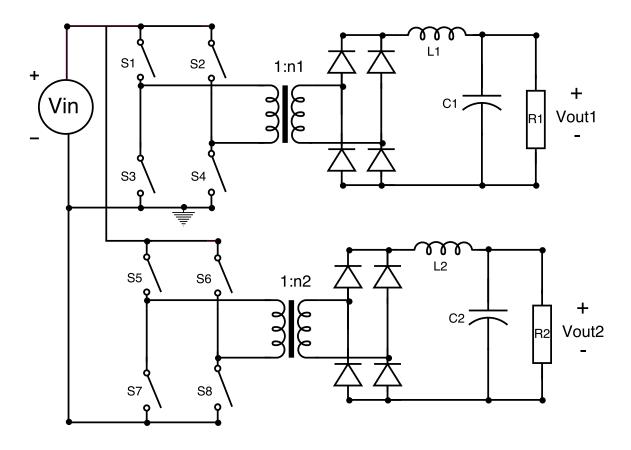

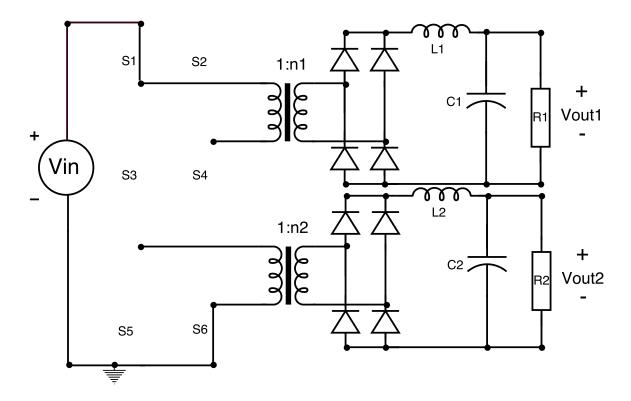

A full-bridge dc-dc converter is shown in Fig. 2.1. The converter has a single dc source.

Fig. 2.1. Full-bridge Single Input Single Output Dc-dc Converter

The primary side of the transformer consists of four switches to build full-bridge switching circuitry. Transformer turns ratio is 1:n from primary to secondary side. A rectifier and LC filter is used in the secondary side to generate the desired output voltage without distortion and enhance smoothness.

#### 2.2.2 Transfer Function

Control of the converter voltage is dependent on the transfer function of the converter.

$$\frac{Vout}{Vpri} = n * D \tag{2.1}$$

Duty cycle is the fraction or period of time during which the system stays active [45], [46], [47].

### 2.2.3 Switching Signals

The switching signals of the converter need to be such that it generates an ac voltage in the transformer primary winding as the transformer cannot convert a dc voltage. The generated voltage at the primary winding should be such that it can be controlled by changing duty cycle of the signal. The converter has four switches. So the possible switching states are  $2^4 = 16$ . All 16 possible states and the generated voltage at the primary side are showed in table 2.1.

If the primary side is open circuited or shorted, it gives a zero voltage. State number 10 generates a positive voltage equal to the source voltage. Similarly, the seventh state generates a negative source voltage. So while taking the switching states for consideration, state 7 and state 10 are must be included in the desired states.

Also while choosing the zero voltage states it should be such that it makes the boolean expression less complicated and compact to implement. The number of logic gates used should also made optimum.

Table 2.1. All Possible States of the Four Switches

| State | Q1 | Q2 | Q3 | Q4 | $V_{Pri}$ |

|-------|----|----|----|----|-----------|

| 1     | 0  | 0  | 0  | 0  | 0         |

| 2     | 0  | 0  | 0  | 1  | 0         |

| 3     | 0  | 0  | 1  | 0  | 0         |

| 4     | 0  | 0  | 1  | 1  | 0         |

| 5     | 0  | 1  | 0  | 0  | 0         |

| 6     | 0  | 1  | 0  | 1  | 0         |

| 7     | 0  | 1  | 1  | 0  | -Vin      |

| 8     | 0  | 1  | 1  | 1  | 0         |

| 9     | 1  | 0  | 0  | 0  | 0         |

| 10    | 1  | 0  | 0  | 1  | Vin       |

| 11    | 1  | 0  | 1  | 0  | 0         |

| 12    | 1  | 0  | 1  | 1  | 0         |

| 13    | 1  | 1  | 0  | 0  | 0         |

| 14    | 1  | 1  | 0  | 1  | 0         |

| 15    | 1  | 1  | 1  | 0  | _         |

| 16    | 1  | 1  | 1  | 1  | 0         |

## 2.2.4 Generation Gating Signals

The states that are considered for the generation of gating signals are shown in table 2.2. The voltage goes from positive to negative and stay as zero in between so that the duty cycle is well defined. From equation 2.2, it can be seen that the ratio of output voltage to input voltage is directly proportional to the duty cycle. So if the duty cycle is changed then the output voltage will change accordingly. So the time the voltage keeps a value (positive and negative) should be increased with increased duty cycle and the time of zero voltage

Table 2.2. States Considered to Generate the Gating Signals

| Q1 | Q2 | Q3 | Q4 | $V_{Pri}$ |

|----|----|----|----|-----------|

| 1  | 0  | 0  | 1  | Vin       |

| 1  | 1  | 1  | 1  | 0         |

| 0  | 1  | 1  | 0  | -Vin      |

| 1  | 1  | 1  | 1  | 0         |

needs to be decreased at the same time. Similarly for decreased duty cycle, time of the signal keeping a value (positive and negative) should be decreased and the time of zero voltage needs to be increased during that state.

Table 2.3. Generating the Four Required Signals

| Sig1 | Sig2 | !Sig2 | $Sig1 \overline{Sig2}=Q1=Q4$ |

|------|------|-------|------------------------------|

| 1    | 1    | 0     | 1                            |

| 1    | 0    | 1     | 1                            |

| 0    | 1    | 0     | 0                            |

| 0    | 0    | 1     | 1                            |

| Sig1 | Sig2 | $\overline{\text{Sig1}} \overline{\text{Sig2}}=\text{Q2}=\text{Q3}$ |

|------|------|---------------------------------------------------------------------|

| 0    | 0    | 1                                                                   |

| 0    | 1    | 1                                                                   |

| 1    | 0    | 0                                                                   |

| 1    | 1    | 1                                                                   |

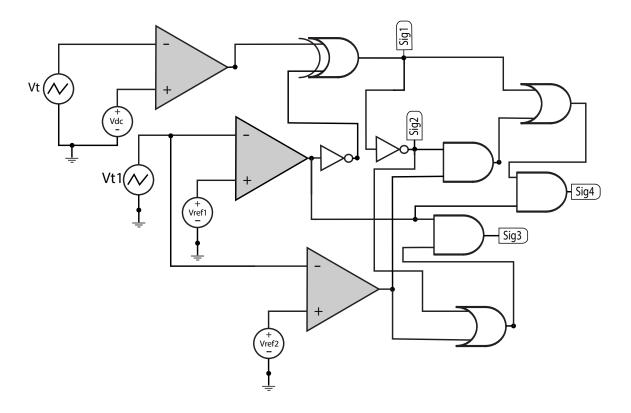

The required switching signals can be generated from two signals Sig1 and Sig2. Signals Q1 and Q4 are same. Similarly signals Q2 and Q3 are same. Signal-1 can be generated

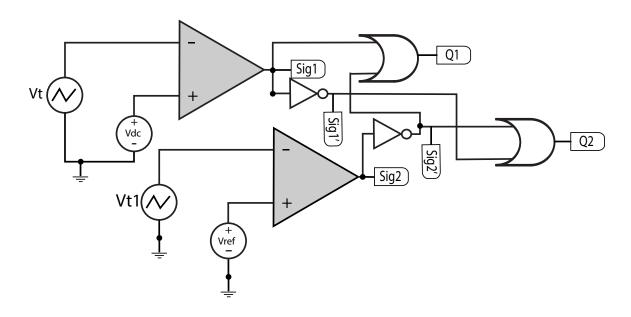

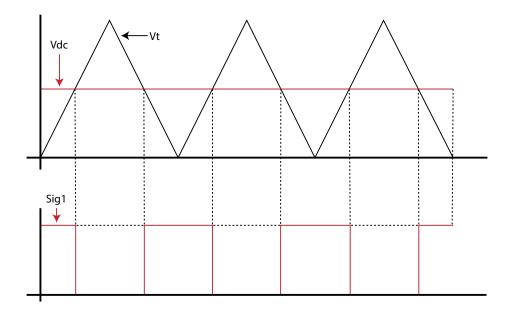

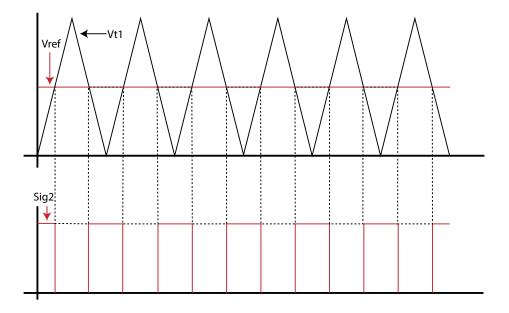

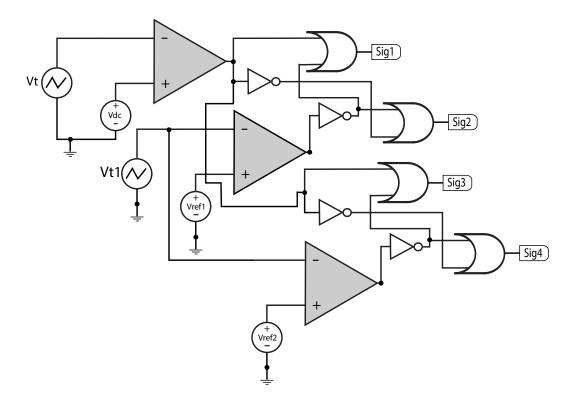

by comparing a triangular wave with a dc voltage using an op-amp. The pulse width modulation (PWM) is a traditional technology that is used in the switching mode power converter to control and regulate the output power [48]. The analog implementation of PWM, also known as naturally sampled PWM, is simpler compared to other methods and it only the generation of a suitable carrier and a comparator [49]. Figure 2.2 shows the gating cir-

Fig. 2.2. Logic Circuit to Generate Switching Signals

cuitry to generate the switching signals. As can be seen from figure 2.2, the triangular wave is connected to the inverting input of the operational amplifier and the dc voltage which is a constant voltage with half the amplitude of the triangular wave is connected to the non-inverting input of the operational amplifier.

When Vdc is greater than the triangular voltage Vt, the op-amp produces a positive voltage. When Vt is greater than Vdc, it gives zero voltage as the non-inverting input node is connected to Vt. So it generates an output pulse every time Vdc is greater than Vt. Sig2 is generated similarly. The reference voltage Vref, controls the duty cycle. If the magnitude of Vref is increased, then the duration it is greater than Vt will increase. Hence

Fig. 2.3. Generation of Sig1 from a Triangular Wave and a Dc Voltage

Fig. 2.4. Generation of Sig2 from a Triangular Wave and a Dc Voltage

the duty cycle is increased. Using the same technique, if less duty cycle is required, then the magnitude of the reference voltage is decreased.

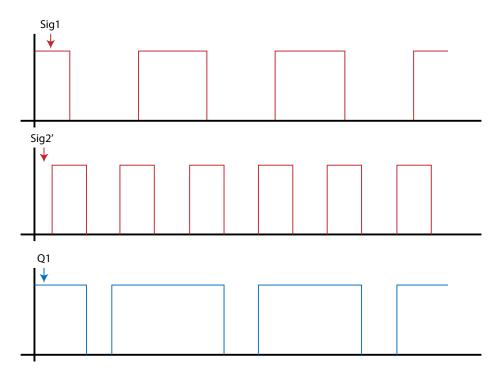

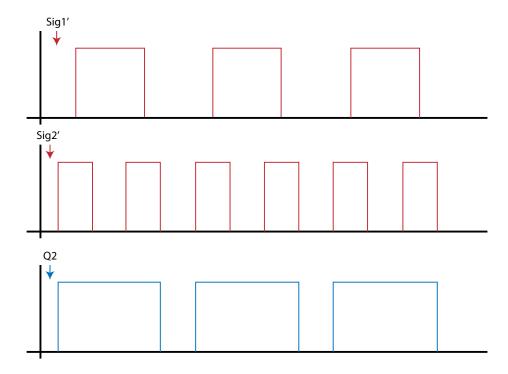

Sig1' is found by passing Sig1 through a **not** gate and Sig2' is found by passing Sig2 through a **not** gate. Q1 is generated by taking **or** of Sig1 and the inverse of Sig2. That

means when both of the signals are zero it will generate zero. Otherwise if either of both of them have value, it will keep generating values. The generation of the switching signal is showed in figure 2.5.

The signal Q2 is generated by passing both of the inverse of Sig1 and Sig2 through an **or** gate. The signal wave-shapes to generate Q2 is shown in figure 2.6.

Fig. 2.5. Generation of Q1 from Sig1 and Sig2

### 2.3 Single Input Dual Output Dc-dc Converter

In [50], a single input dual output converter was presented but it requires control system constituting both duty cycle and frequency. Changing duty cycle is easily possible but changing frequency to control a load could be a complex and cost inducing method. In addition to it, the lower load was loosely connected to the transformer primary winding. So to utilize similar control method for both of the loads, the conventional dc-dc converter to supply two separate loads is explored in this section.

Fig. 2.6. Generation of Q2 from Sig1' and Sig2'

## 2.3.1 Converter Configuration

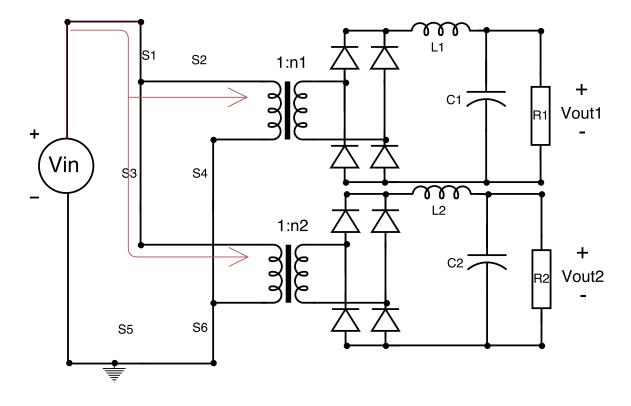

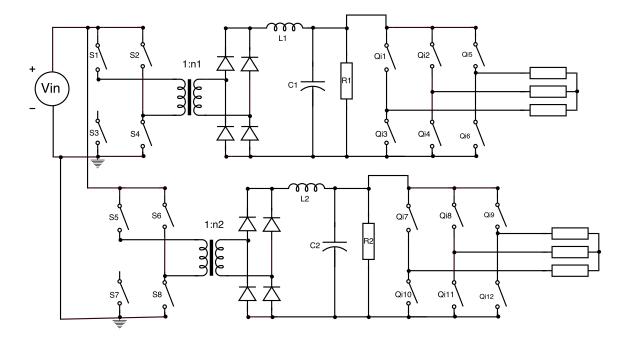

To implement using the conventional single input single output circuitry, supplying dual output from a single source requires a parallel connection from the source. This ensures that both of the load can have the whole source voltage in the primary side. The converter is shown in figure 4.1. The input voltage is Vin and there are two loads R1 and R2 connected to it. There are four switches for each of the primary side and hence there are eight switches altogether.

## 2.3.2 Gating Signal Circuitry

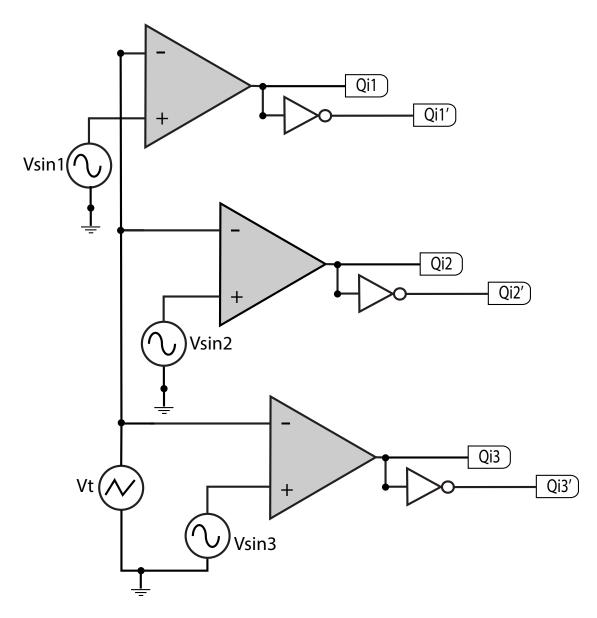

As discussed in the previous section, the switching signals are generated using logic gates. Figure 2.8 shows the logic circuit that generates the gating signals.

Three operational amplifiers generate the required pulses. From these signals through the **not** gates and **or** gates, four gating signals for the eight switches are generated.

Fig. 2.7. Full-bridge Single Input Dual Output Dc-dc Converter

The signal Sig1 is the switching signal for the switches S1 and S2, Sig2 is for the switches S2 and S3, Sig3 is for the switches S5 and S8 and Sig4 is for the switches S6 and S7 in figure 4.1.

# 2.3.3 Transfer Function

If the turns ratios of the transformers are n1 and n2 and duty cycles of the signals are D1 and D2 for load1 and load2 respectively, then the transfer functions are:

$$\frac{Vout1}{Vpri1} = n1 * D1 \tag{2.2}$$

Fig. 2.8. Logic Circuit to Generate Switching Signals

$$\frac{Vout2}{Vpri2} = n2 * D2 \tag{2.3}$$

In these cases, the primary side voltages can reach the value of the input voltage.

## 2.4 Dc-Ac Converter

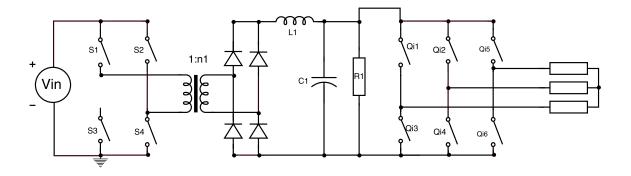

For the applications where ac output is required, an inverter portion is integrated at the load side in order to provide alternating current. The typical converter that converts the dc input to a required ac value is shown in figure 2.9.

Fig. 2.9. Conventional Single-Input Single-output Inverter

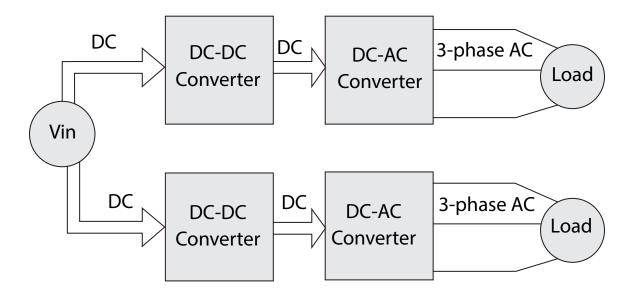

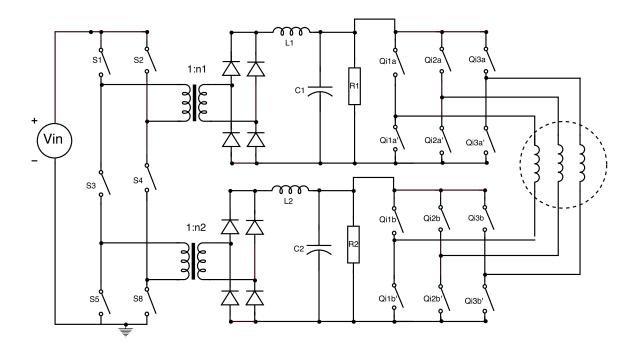

Figure 2.9 presents the converter with only one input and one output. Like the previous section, if the converter is made to supply two separate loads, then the traditional configuration looks like the one in figure 2.10.

Fig. 2.10. Single-input Dual-output Dc-dc-ac Converter with Eight Switches

The single input converter that supplies two ac loads in figure 2.10 is consists of eight switches in total. For this circuit configuration, the gating signals for the dc-dc converters are similar to the ones generated in an earlier section. The switching signals of the eight switches in the left side of the design are generated using a similar circuit shown in figure 2.8.

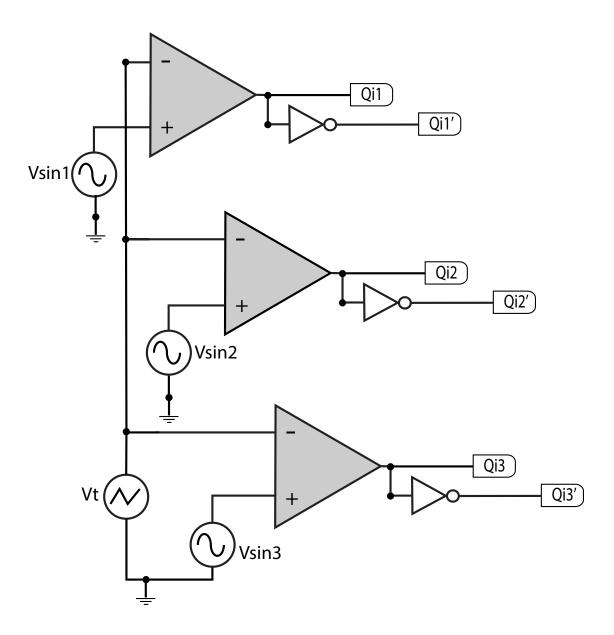

Fig. 2.11. Switching Signal Generation of Dc-ac Converter

For the generation of six set of signals at the dc-ac converter side, the similar gating signal generation circuit for a conventional inverter is used. The circuitry is shown in figure 5.6. These generated signals can be used for both of the loads.

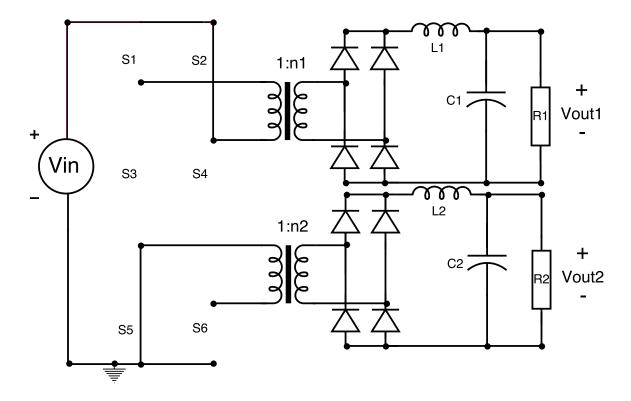

## 3. PROPOSED DC-DC CONVERTER

#### 3.1 Introduction

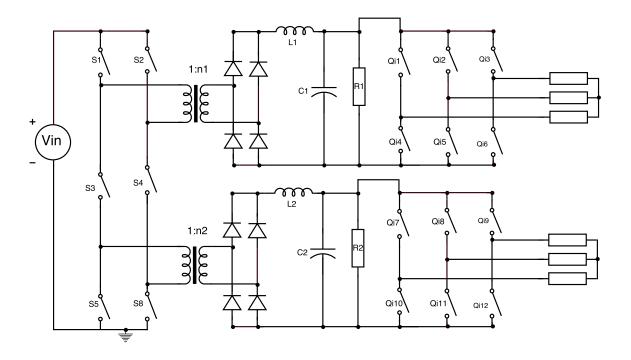

The proposed dc-dc converter have reduced number of switches comparing to the conventional single input dual output converter. As discussed in the previous chapter, the conventional single input dual output dc-dc converter requires eight switches in total to operate two loads separately. In the proposed converters several possibilities were explored to reduce the number of switches. Then it was designed with only six switches and a unique switching signal was proposed to reach the optimum number of logic gates to generate the switching signals.

#### 3.2 Motivation

It was explained in [51], using three switches instead of four switches in the dual output buck converter is able to save silicon area with suitable design of power switches. Similarly for a full-bridge dc-dc converter, if a dual output converter can be designed with reduced number of switches, it should be able to reduce cost in implementation of the regulator switches. In [52], three switch dual output buck converter was explored to alleviate space and platform cost in PC platform that hosts various subsystems such as the central processing unit (CPU), memory and I/O control hubs, the memory subsystem, graphics, audio, LAN etc. Because with increased features, the power delivery network is required to be able to supply different voltage levels which increases cost, requires more space and consequently reduces efficiency. For this kind of PC platform, compact and high efficiency power conversion system is needed.

In the field of renewable energy, the power electronic system and hence high efficiency power conversion system is also a necessity. Due to the increased demand of power generation, the utilization of renewable energy has increased and has become more popular over the traditional fossil resources [53]. The drop in photo-voltaic pricing trend is demonstrated in [54]. Not only the use of renewable energy is cost effective than the diesel fuel, but also it has increased reliability [55]. For dispersed power generation systems, power electronic interfaces are a necessity [56]. Especially for the integration of renewable energy sources to the grid [57]. To increase robustness of these interfaces many configurations have been proposed. To reduce power coupling and improve system stability in distributed generation unit, implementation of virtual impedance is found useful [58].

In microgrid system, cluster of small energy generators such as solar cells, fuel cells, wind turbine along with electrical loads exist within the main grid that includes embedded management and control system which requires power electronic converters [59]. Detailed analysis at power converter level of microgrid structures and control techniques were discussed in [60]. Power electronic interface for distributed energy has the following advantages:

- 1. By mitigating harmonic elements and maintaining power factor within range, PE interface improves power quality. In addition to it, PE interface ensures uninterrupted power flow which have much faster response time than non-PE based system especially for sensitive loads and induction and synchronous generator systems [61].

- 2. In radial distribution system, PE system in voltage regulation has the benefit of controlling voltage and reactive power at the generation [62].

- 3. By employing enhanced phase locked loop [EPLL] as the synchronization method provides more frequency adaptivity with unbalanced or polluted signals that has noise, harmonics etc. and with variable frequency environments [63].

- 4. Reliability analysis and was conducted in [64] through reliability prediction metrics by evaluating reliability, failure rate, mean time to failure (MTTF), mean time to repair (MTTR) and availability. Then the improvement of reliability of the system was provided by component assessments and fault analysis which is possible in power electronic system.

Power electronic converters are used to convert energy suitable for distribution. In solar PV micro-inverter, the generated input voltage is required to be boosted to a higher voltage level for practical use [65]. Especially in module integrated PV micro-inverters. The feasibility of dispatchable converters was presented in the researches in [66] and [67]. High step-up converters [15] are required for these kind of applications.

For various applications like electric tractor locomotives or elevators, doubly fed machines are required to operate from one input source [27]. Multiple outputs also wide range applications in hybrid electric vehicles [28], LED lighting [29], dc based nano-grids [30], stand-by power supplies etc. [31], [32]. In addition to it, the setup where to loads can be operated from the same source reduce the bulkiness of the conventional converters and provide more compactness, cost effectiveness [33] and have higher efficiency [34]. A single input dual output buck converter is presented and utilization of power switches are shown in [35] and in [36], it was presented for both unidirectional and bidirectional operations.

Isolated converter is preferred over conventional one as it provides full dielectric isolation between input and output. In case of internal failure, the input voltage is prevented to be transmitted to the output. In addition to it, this type of converters protects the person handling it.

#### 3.3 Design Requirements

From the motivation to design a novel isolated dc-dc converter, the converter was designed to meet the following specifications:

- 1. It has the same transfer function as the conventional one so that the output is similar.

- 2. The output voltages can be controlled separately with load requirement.

- 3. Switching and conduction losses are less than the conventional one.

## 3.4 Converter Design and Layout

To ensure the control of the loads separately, each primary side requires four switches in the conventional one. The upper pairs of switches connects the positive input and the lower pairs ensure the connection to ground.

Fig. 3.1. Proposed Single Input Dual Output Dc-dc Converter

The number of switches can be reduced by using only a pair of switch in the middle for both of the loads instead of the lower pair of switches of the upper load and upper pair of switches in the lower load. The layout of the converter is shown in figure 3.1.

## 3.5 Switching States

The next challenge of the design procedure is finding the correct switching state for the converter to supply regulated voltage. By changing the switching states, the converter can

have serial or parallel connection for both of the loads. For six switches with two states (on and off), the converter can have  $2^6 = 64$  states. By changing the states of each switch, the voltage at the primary sides are calculated for all 64 states.

Table 3.1.: All topological states

| State | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Vpri1 | Vpri2 |

|-------|----|----|----|----|----|----|-------|-------|

| 1     | 0  | 0  | 0  | 0  | 0  | 0  | 0     | 0     |

| 2     | 0  | 0  | 0  | 0  | 0  | 1  | 0     | 0     |

| 3     | 0  | 0  | 0  | 0  | 1  | 0  | 0     | 0     |

| 4     | 0  | 0  | 0  | 0  | 1  | 1  | 0     | 0     |

| 5     | 0  | 0  | 0  | 1  | 0  | 0  | 0     | 0     |

| 6     | 0  | 0  | 0  | 1  | 0  | 1  | 0     | 0     |

| 7     | 0  | 0  | 0  | 1  | 1  | 0  | 0     | 0     |

| 8     | 0  | 0  | 0  | 1  | 1  | 1  | 0     | 0     |

| 9     | 0  | 0  | 1  | 0  | 0  | 0  | 0     | 0     |

| 10    | 0  | 0  | 1  | 0  | 0  | 1  | 0     | 0     |

| 11    | 0  | 0  | 1  | 0  | 1  | 0  | 0     | 0     |

| 12    | 0  | 0  | 1  | 0  | 1  | 1  | 0     | 0     |

| 13    | 0  | 0  | 1  | 1  | 0  | 0  | 0     | 0     |

| 14    | 0  | 0  | 1  | 1  | 0  | 1  | 0     | 0     |

| 15    | 0  | 0  | 1  | 1  | 1  | 0  | 0     | 0     |

| 16    | 0  | 0  | 1  | 1  | 1  | 1  | 0     | 0     |

| 17    | 0  | 1  | 0  | 0  | 0  | 0  | 0     | 0     |

| 18    | 0  | 1  | 0  | 0  | 0  | 1  | 0     | 0     |

| 19    | 0  | 1  | 0  | 0  | 1  | 0  | 0     | 0     |

| 20    | 0  | 1  | 0  | 0  | 1  | 1  | 0     | 0     |

| 21    | 0  | 1  | 0  | 1  | 0  | 0  | 0     | 0     |

| 22    | 0  | 1  | 0  | 1  | 0  | 1  | 0     | 0     |

continued on next page

Table 3.1.: continued

| State | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Vpri1 | Vpri2 |

|-------|----|----|----|----|----|----|-------|-------|

| 23    | 0  | 1  | 0  | 1  | 1  | 0  | 0     | -Vin  |

| 24    | 0  | 1  | 0  | 1  | 1  | 1  | 0     | 0     |

| 25    | 0  | 1  | 1  | 0  | 0  | 0  | 0     | 0     |

| 26    | 0  | 1  | 1  | 0  | 0  | 1  | 0     | 0     |

| 27    | 0  | 1  | 1  | 0  | 1  | 0  | -Vin  | 0     |

| 28    | 0  | 1  | 1  | 0  | 1  | 1  | -Vin  | 0     |

| 29    | 0  | 1  | 1  | 1  | 0  | 0  | 0     | 0     |

| 30    | 0  | 1  | 1  | 1  | 0  | 1  | 0     | 0     |

| 31    | 0  | 1  | 1  | 1  | 1  | 0  | -Vin  | -Vin  |

| 32    | 0  | 1  | 1  | 1  | 1  | 1  | -Vin  | 0     |

| 33    | 1  | 0  | 0  | 0  | 0  | 0  | 0     | 0     |

| 34    | 1  | 0  | 0  | 0  | 0  | 1  | 0     | 0     |

| 35    | 1  | 0  | 0  | 0  | 1  | 0  | 0     | 0     |

| 36    | 1  | 0  | 0  | 0  | 1  | 1  | 0     | 0     |

| 37    | 1  | 0  | 0  | 1  | 0  | 0  | 0     | 0     |

| 38    | 1  | 0  | 0  | 1  | 0  | 1  | Vin   | 0     |

| 39    | 1  | 0  | 0  | 1  | 1  | 0  | 0     | 0     |

| 40    | 1  | 0  | 0  | 1  | 1  | 1  | Vin   | 0     |

| 41    | 1  | 0  | 1  | 0  | 0  | 0  | 0     | 0     |

| 42    | 1  | 0  | 1  | 0  | 0  | 1  | 0     | Vin   |

| 43    | 1  | 0  | 1  | 0  | 1  | 0  | 0     | 0     |

| 44    | 1  | 0  | 1  | 0  | 1  | 1  | 0     | 0     |

| 45    | 1  | 0  | 1  | 1  | 0  | 0  | 0     | 0     |

| 46    | 1  | 0  | 1  | 1  | 0  | 1  | Vin   | Vin   |

| 47    | 1  | 0  | 1  | 1  | 1  | 0  | 0     | 0     |

continued on next page

Table 3.1.: continued

| State | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Vpri1 | Vpri2 |

|-------|----|----|----|----|----|----|-------|-------|

| 48    | 1  | 0  | 1  | 1  | 1  | 1  | Vin   | 0     |

| 49    | 1  | 1  | 0  | 0  | 0  | 0  | 0     | 0     |

| 50    | 1  | 1  | 0  | 0  | 0  | 1  | 0     | 0     |

| 51    | 1  | 1  | 0  | 0  | 1  | 0  | 0     | 0     |

| 52    | 1  | 1  | 0  | 0  | 1  | 1  | 0     | 0     |

| 53    | 1  | 1  | 0  | 1  | 0  | 0  | 0     | 0     |

| 54    | 1  | 1  | 0  | 1  | 0  | 1  | 0     | 0     |

| 55    | 1  | 1  | 0  | 1  | 1  | 0  | 0     | -Vin  |

| 56    | 1  | 1  | 0  | 1  | 1  | 1  | 0     | 0     |

| 57    | 1  | 1  | 1  | 0  | 0  | 0  | 0     | 0     |

| 58    | 1  | 1  | 1  | 0  | 0  | 1  | 0     | Vin   |

| 59    | 1  | 1  | 1  | 0  | 1  | 0  | 0     | 0     |

| 60    | 1  | 1  | 1  | 0  | 1  | 1  | 0     | 0     |

| 61    | 1  | 1  | 1  | 1  | 0  | 0  | 0     | 0     |

| 62    | 1  | 1  | 1  | 1  | 0  | 1  | Vin   | 0     |

| 63    | 1  | 1  | 1  | 1  | 1  | 0  | 0     | 0     |

| 64    | 1  | 1  | 1  | 1  | 1  | 1  | 0     | 0     |

All 64 topological states and the respective primary side voltages are shown in table 3.1.

# 3.6 Gating Signals

Careful consideration was made during choosing the desired states among the 64 states. There are several ways to choose the switching signals. All these ways will be discussed in this section.

### 3.6.1 Serially Connected Loads Operate Together

One configuration of switching signals connect the loads in series. If both loads operate at the same time then the source voltage gets divided among the primary sides voltages. None of the loads can have the primary voltage as Vdc. It is always less than Vdc and very difficult to control.

If both load1 and load2 require reduced voltage, then if the controlling duty cycle for load1 is reduced it provides reduced voltage at Vpri1. But at the same time it will force to increase the voltage at Vpri2 regardless of the decreased duty cycle of load2 controlling signal. Because from Kirchhoff's voltage law, after having a lesser voltage drop at load1, the rest of the voltage from Vdc have to drop at load2 for a balanced connection. The same difficulty will be faced in case of the need of increased voltage. If one or both of the loads have a certain limitation of input voltage, then this operation of uncontrolled load will lead to damage and may bear serious safety issues.

In addition to it, this connection fails to utilize the whole source voltage at primary side. To achieve the required voltage level at secondary sides of the transformers the turns ratios are needed to be much greater than the conventional one due to small primary voltage.

At the initial stage of this converter design, gating signals for this configuration was selected and generated using logic circuitry. Then the output was predicted by drawing equivalent circuits and calculation. The results were verified by simulation. And it possessed high risk and less efficiency for practical use as expected.

# 3.6.2 Serially Connected Loads Operate Separately

The previous connection had the disadvantage of not getting the whole Vdc at each of the primary sides. One way to avoid the problem can be to choose a gating signal in such a way that the loads do not operate at the same time. In that way one of the loads will have the whole input voltage at the primary side and the other will have zero. For example if the first load has zero voltage at the primary side, the second one will have +Vdc or -Vdc at the primary side and vice versa. For this state the desired states are chosen from table 3.1.

Load-1 with positive primary voltage and load-2 with zero primary voltage can be generated from switching state 38, 40, 48 or 62. Then load-1 with zero primary voltage and load-2 with positive voltage can be generated from the switching state 42 or 58. Load-1 with negative primary voltage and load-2 with zero primary voltage can be generated from switching state 27, 28 or 32. Then load-1 with zero primary voltage and load-2 with negative voltage can be generated from the switching state 23 or 56.

Table 3.2. States Considered to Generate the Gating Signals

| Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | $V_{Pri1}$ | $V_{Pri2}$ |

|----|----|----|----|----|----|------------|------------|

| 1  | 0  | 0  | 1  | 0  | 1  | Vdc        | 0          |

| 0  | 1  | 0  | 1  | 1  | 0  | 0          | Vdc        |

| 0  | 1  | 1  | 0  | 1  | 0  | -Vdc       | 0          |

| 1  | 0  | 1  | 0  | 0  | 1  | 0          | -Vdc       |

Several attempts were made with different configurations of the states. The most convenient one to implement is presented in table 3.2. The selected states to generate the gating signals are 38, 23, 27 and 42. From the table, it is observed that switching signal Q1 and Q6 are same and switching signals Q2 and Q5 are same. Also the signals Q3 and Q4 are inverse to each other.

Table 3.3. Logic Table to Generate the Gating Signals

| Q4 | Sig2 | Q4\(\propto\)Sig2=Q2=Q5 | !Q2=Q1=Q6 | !Q4=Q3 |

|----|------|-------------------------|-----------|--------|

| 1  | 1    | 0                       | 1         | 0      |

| 1  | 0    | 1                       | 0         | 0      |

| 0  | 1    | 1                       | 0         | 1      |

| 0  | 0    | 0                       | 1         | 1      |

Table 3.3 presents the generation of gating signals using logic gates. Sig2 is a signal similar to Q4 but has double the frequency of Q4. These two signals can be used to generate the signal Q2 through **xor**. The signal Q1 and Q3 can be generated by simply using **not** in the signals Q2 and Q4 respectively. As mentioned before, Q5 is the same signal as Q2 and Q6 is the same signal as Q1.

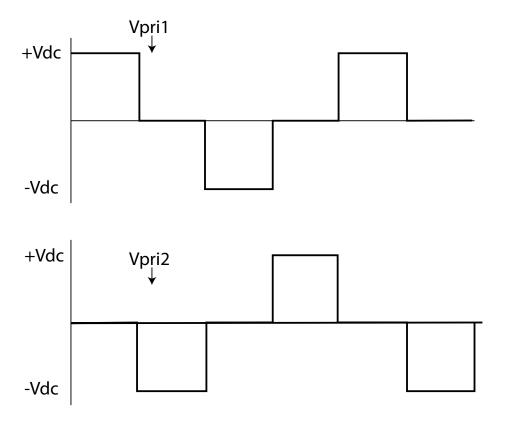

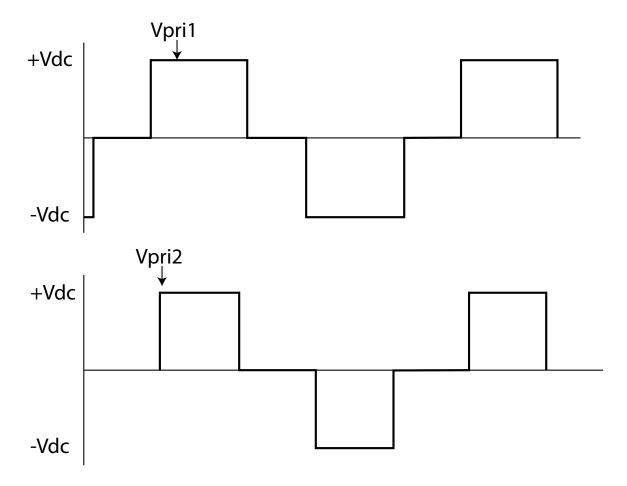

Fig. 3.2. Primary Side Voltages of the Loads for Series Connection

If the signals are implemented, the voltages at primary sides of the loads will be like the one in figure 3.2. In this case, the problem faced about having the source voltage at the primary side in the previous design was eliminated. As the loads do not operate at the same time, the input voltage is present with the whole magnitude in the primary side voltage.

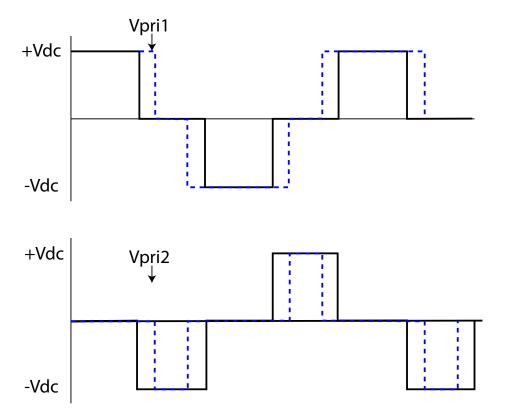

If the generated input voltage is lesser than the required input voltage, then the output voltage at the loads will be less too. In that case, to reach the required voltage level, the duty cycle needs to be boosted. Figure 3.3 shows the primary sides for the loads if the duty

Fig. 3.3. Primary Side Voltages with Increased Duty Cycle for Load-1

cycle for load-1 in increased. From the figure, it is observed that, when the duty cycle for load-1 increases, to ensure the voltage level Vdc at the primary side for the load-1, the duty cycle for load-2 has to be decreased. If the duty cycle for load-1 is same as the before, then for a particular time, both switches that control the loads will be on. Hence the source voltage will get divided among the loads. The problem of not having Vdc as primary side voltage like the previous design will still remain. Also depending on the load condition, the voltage level will fluctuate and hence will be difficult to control. Similarly, if the duty cycle for load-2 in needed to be increased, then duty cycle for load-1 must have to decrease to ensure consistent voltage at primary sides. So this arrangement lead to either compensate one of the loads for the other or have different unwanted and unpredictable voltage levels at the primary sides. It also makes the duty cycles dependent on each other as the load that

is being compensated is forced to a smaller duty cycle to ensure larger duty cycle to the other. Similar situations are applicable when lower voltage is required.

This configuration will work great for the situations where both of the loads are complete opposite in terms of voltage requirements and are somewhat dependent on each other in increasing and decreasing load requirements.

So a decision can be made from this design that although the loads can operate with different duty cycle and hence can generate different levels of output voltage, the problem with independent control of the loads still prevalent during this connection.

### 3.6.3 Parallel Connection of the Load

From another combination from table 3.1, a parallel connection of the loads can be made. For parallel connection, the positive node of the source voltage is connected to the same upper or lower node of both of the loads. Similarly the ground is connected to the same upper or lower node of both of the loads.

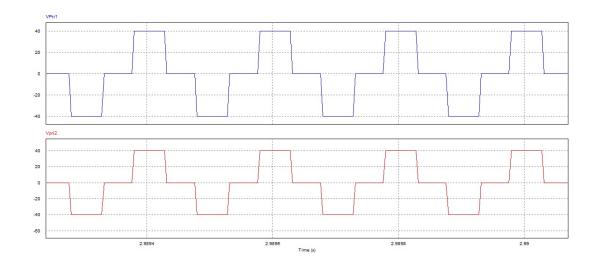

During this configuration, both loads can operate at the same time with separate duty cycles. Figure 3.4 shows the primary side voltages of both of the loads. It can be seen that load-1 has greater duty cycle than load-2 and they are capable of operating independently.

This connection solves the problem of dependency on each load and the loads does not have to compensate for the primary side voltages. Therefore, for this design, this connection was chosen.

### 3.7 Selection of Gating Signal for the Proposed Converter

As discussed in the previous section, the parallel connection was chosen for this design. The states should be chosen such that the switches operate such that the loads get connected in parallel rather than in serial.

From table 3.1, during state 46 both of the loads have positive source voltage at primary sides and during state 31, they have negative source voltage at the primary side. So, these

Fig. 3.4. Primary Side Voltages of the Loads for Parallel Connection

two states must be taken into consideration as they definitely ensures parallel connection of the loads.

Table 3.4 shows the desired switching states for generating the gating signals. Other two states, where the loads have zero voltage at primary sides, are chosen such that the logic circuitry to generate the switching signals is convenient. Switching signal Q1 and Q2 are simply the inverse to each other. If signal Q1 can be generated then passing Q1 through a NOT gate will generate the signal Q2.

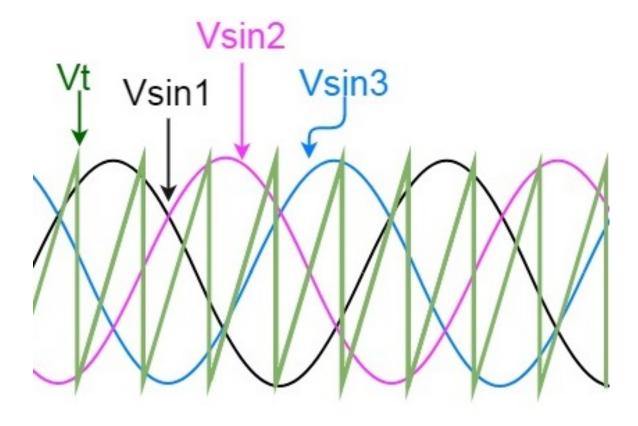

Two signals Sig1 and Sig2 are utilized to generate the other signals similar to the one in serial connection. Sig1 is generated by comparing a triangular wave with a reference dc

Table 3.4. Desired Switching States

| Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Vpri1 | Vpri2 |

|----|----|----|----|----|----|-------|-------|

| 1  | 0  | 1  | 1  | 0  | 1  | Vdc   | Vdc   |

| 0  | 1  | 0  | 0  | 1  | 0  | 0     | 0     |

| 0  | 1  | 1  | 1  | 1  | 0  | -Vdc  | -Vdc  |

| 1  | 0  | 0  | 0  | 0  | 1  | 0     | 0     |

voltage. Sig2 is generated in a similar fashion but from a triangular wave with double the frequency than the one used to generate Sig1.

Table 3.5.

Generation of the Switching Signals for the Switches Q1 and Q2

| Sig1 | Sig2' | (Sig1\big2')Q1 | <del>Q</del> 1=Q2 |

|------|-------|----------------|-------------------|

| 1    | 0     | 1              | 0                 |

| 1    | 1     | 0              | 1                 |

| 0    | 0     | 0              | 1                 |

| 0    | 1     | 1              | 0                 |

Sig2' is the inverse of Sig2. Signal Q1 can be generated by passing the signals Sig1 and Sig2' through an XOR gate. Generation of Q1 and Q2 are shown in table 3.5.

Although from table 3.4, it may seem like the signal Q3 is same as Sig2, but this signals contribute to the duty cycle for primary side voltages. So they are needed to be controlled separately.

Table 3.6 shows how the signal Q3 can be generated from Sig2 and Q2. First these signals are passed through an OR gate then an intermediate signal Sig3 is generated. From Sig2 and Sig3, signal Q3 is found.

Table 3.6. Generation of the Switching Signals for the Switch Q3 (Initial)

| Q2 | Sig2 | (Q2 Sig2)Sig3 | (Sig2&Sig3)Q3 |

|----|------|---------------|---------------|

| 0  | 1    | 1             | 1             |

| 1  | 0    | 1             | 0             |

| 1  | 1    | 1             | 1             |

| 0  | 0    | 0             | 0             |

From the properties of boolean algebra [68] to expand the signals we get,

$$Q2 = \overline{Sig1.\overline{Sig2'} + \overline{Sig1}.Sig2'}$$

(3.1)

$$= Sig1.Sig2 + \overline{Sig1}.\overline{Sig2}$$

(3.2)

Using the expanded value of the signal Q1 from equation (3.2),

$$Q3 = (Sig2 + Q1).Sig2 (3.3)$$

$$= (Sig2 + Sig1.Sig2 + \overline{Sig1}.\overline{Sig2}).Sig2$$

(3.4)

$$= (Sig2(Sig1 + 1) + \overline{Sig1}.\overline{Sig2}).Sig2$$

(3.5)

$$= (Sig2.1 + \overline{Sig1}.\overline{Sig2}).Sig2$$

(3.6)

$$= (Sig2 + 0).Sig2 (3.7)$$

$$Q3 = Sig2 (3.8)$$

From equation (3.8), it can be seen that the signal Q3 has been reduced to a single term. Apparently it may seem that simply using the generated signal Sig2 as the switching signal at the third switch will provide the desired switching cases. But in this case, to generate the proper primary side voltages, require the switch to turn on and off for specific times depending on both of the loads. The above calculations will work only if the duty cycle for the converters are same. But in most of the practical cases they are not same and it impedes the goal of this configuration. So the signal used to control the duty cycle of the second load, Sig2'2 is used too to generate the signal.

Table 3.7. Generation of the Switching Signals for the Switch Q3 (Final)

| Q2 | Sig2'2 | (Sig2'2 Q2)Sig3 | (Sig2&Sig3)Q3 |

|----|--------|-----------------|---------------|

| 0  | 1      | 1               | 1             |

| 1  | 0      | 1               | 0             |

| 1  | 1      | 1               | 1             |

| 0  | 0      | 0               | 0             |

Table 3.7 shows the ways to generate the signal for switch Q3 by using both the controlling signal for load-1 and load-2.

Although signal Q4 looks same as signal Q3 from the table, but as these switches are in the middle, they work for controlling both the upper load and lower load. So their time of operation should be different depending of load-1 and load-2. Also, in this case the signals Sig2 that controls the duty cycle for load-1 and Sig2'2 that controls the duty cycle for load-2 need while generating the switching signal for Q4.

Table 3.8 shows the generation logic for Q4. First an intermediate signal Sig4 is formed from Q2 and Sig2'2. Then from this Sig4 and Q1, another intermediate signal Sig5 is formed using OR gate. Then again from this Sig5 and Sig2, the signal Q4 is generated through an AND gate.

### 3.8 Switching State Diagrams

Equivalent diagrams for different states are shown in this section to show how the converter operates. The duty cycle is the time the load is on. For convenience let, to have duty cycle D1, load-1 needs to operate for Ton1 time and to have duty cycle D2, load-2 needs to operate for Ton2 time when Ts is the whole period.

**State 1** For positive voltage generation at Vpri1, the switches Q1, Q4 and Q6 have to be conducting for Ton1. During this state, switch Q3 conducts for Ton2 time. Only the

Table 3.8. Generation of the Switching Signals for the Switch Q4

| Q2 | Sig2'2 | (Q2(AND)Sig2'2)Sig4 |

|----|--------|---------------------|

| 0  | 1      | 0                   |

| 1  | 0      | 0                   |

| 1  | 1      | 1                   |

| 0  | 0      | 0                   |

| Q1 | (Sig4(OR)Q1)Sig5 | (Sig5(AND)Sig2)Q4 |

|----|------------------|-------------------|

| 1  | 1                | 1                 |

| 0  | 0                | 0                 |

| 0  | 1                | 1                 |

| 1  | 1                | 0                 |

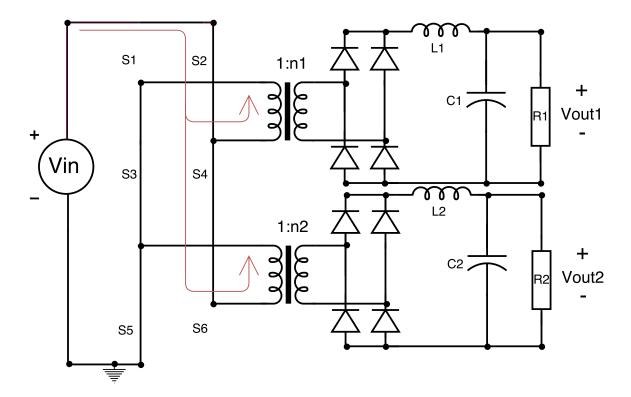

switch Q3 during this time ensures connection of load-2. During Ton2, load 2 has positive voltage on the primary and secondary sides.

This situation is shown in figure 3.5. The parallel connection of the loads ensure positive voltage at both of the primary sides. As can be seen from the figure that when both of the loads are operating, switch S1 and S3 are connected to the same node +Vin and the switches S4 and S6 are connected to the same ground node.

**State 2** Zero voltage can be generated by following several configurations. For this particular configuration, only switches Q2 and Q5 are conducting. As no path is fulfilled, no current flows and the source get disconnected from the load. Hence it results zero voltage. The equivalent circuit without any path to flow current is shown in figure 3.6.

As the switching signals are generated separately, it needs to be ensured that switches Q3 and Q4 are open for (Ts-Ton1) time, so that they don't create any path for current

Text

Fig. 3.5. Equivalent Circuit for the First State

flow and result in unwanted voltage at the loads. The switching signals at Q3 and Q4 have to follow Q1 at this stage.

**State 3** For negative voltage generation, pulses at switches Q2, Q3 and Q5 controls load1. During this time, pulse for Ton2 time at switch Q4, controls operation of load2.

Figure 3.7 shows the equivalent circuit and the direction of current flow during this state. During this state, the switches S3 and S5 are connected to the ground when operate and switches S2, S4 and S6 are connected to the same node as +Vin when operate. So the voltages at primary sides of the loads are

$$0 - (+Vin) = -Vin$$

Fig. 3.6. Equivalent Circuit for the Second State

Thus both of loads have negative voltage at primary sides and the operating time of Q4 ensures the duty cycle for load-2.

**State 4** This state is similar to state-2. Switches Q1 and Q6 are closed without making any circuit path. All other switches have to stay open for the same amount of time as these switches are operating. They need to follow the signal at Q2 for this stage.

Figure 3.8 shows the equivalent circuit for this state. No path is made for the flow of current.

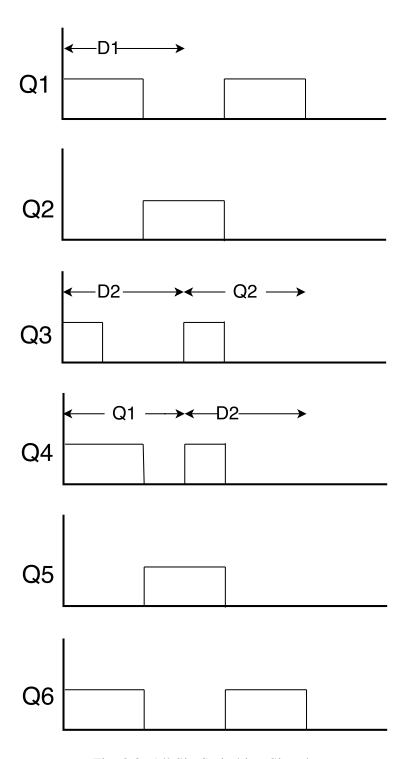

# 3.9 Switching Signal Circuitry

While generating switching signals, a triangular wave is compared with the reference voltage. Another triangular wave is required to control the loads which is of twice the

Fig. 3.7. Equivalent Circuit for the Third State

switching frequency. For output1, the duty cycle can vary up to the maximum, which is 1. But output2 can reach the duty cycle equal to D1. The reference voltage can vary according to the output voltage considering the range.

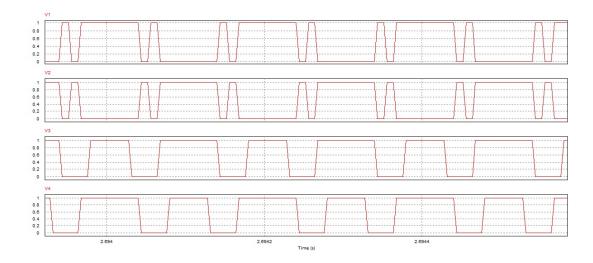

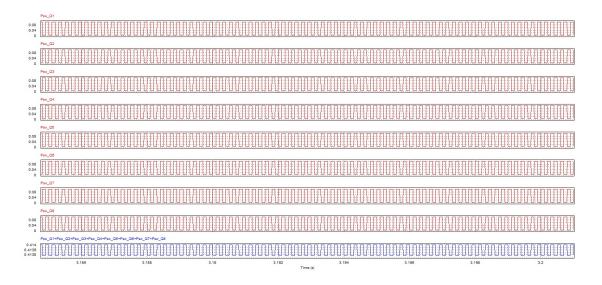

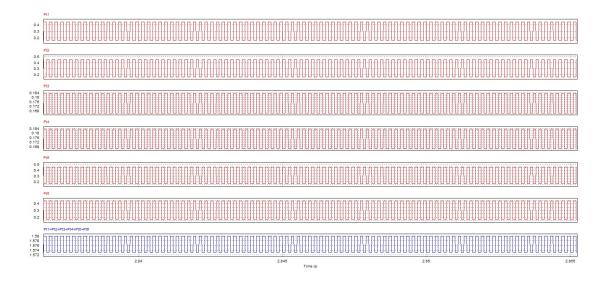

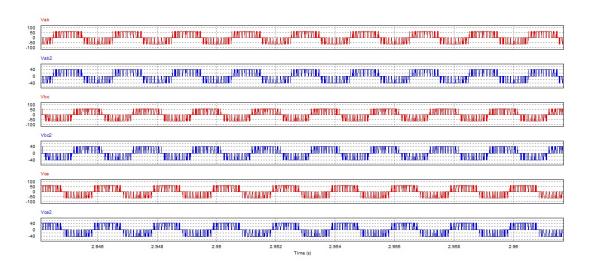

Figure 3.9 shows the all six switching signals of this converter. In this figure Q1 to Q2 are the switching signals for the switches S1 to S6 respectively.

The first switch has the pulse equal to the defined duty cycle for load-1. The signal at the second switch is just inverse to switch-1. In other others, it has a zero value or it is off for the same time as switch-1 is on that is the defined duty cycle for load-1. The signals at the third and fourth switch are a little complicated. The first part of the signal at the third switch operates for the required duty cycle at load-2. It requires keeping the zero value apart from the required operating time. After that instead of repeating the first part again, the signal follows the signal at the second switch for the rest of the time period. The signal

Fig. 3.8. Equivalent Circuit for the Fourth State

at the fourth switch, follows the signal at first switch for the first part. Then it operated for the duty cycle for load-2. The signals at switch-5 is same as the second signal and the signal at switch-6 is same as the first switching signal.

Figure 3.10 shows the gating signal circuitry that generates the switching signals. In the figure, the labels Sig1, Sig2, Sig3 and Sig4 refers to the switching signals at first four switches. As the signals Q5 and Q6 are same as the signals Q2 and Q1 respectively, they were not generated separately using other gating circuits.

Fig. 3.9. All Six Switching Signals

Fig. 3.10. Circuitry to Generate Gating Signals

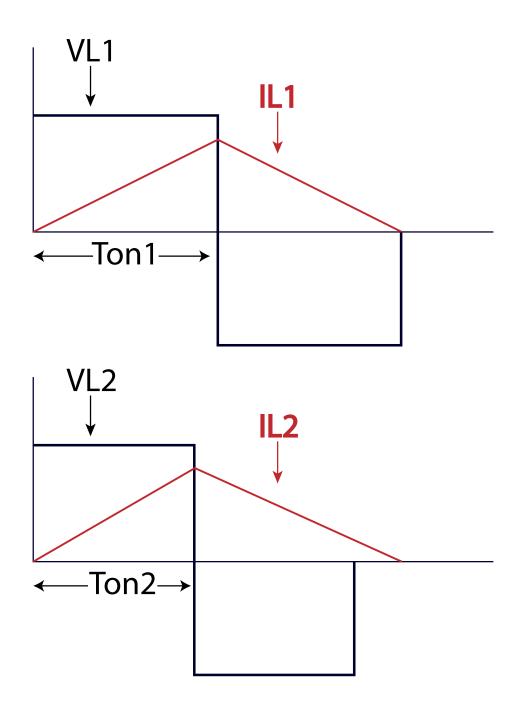

# 3.10 Steady State Analysis

If the turns ratios of the high frequency transformers are n1 for output1 and n2 for output2, then as the voltage of the secondary side is turns ratio times the voltage of the primary side,

$$Vsec1 = n1 * Vpri1$$

$$Vsec2 = n2 * Vpri2$$

For state 1, the switches Q1, Q4 and Q6 are closed for the time Ton1 which controls output1. The switch Q3 is conducting for Ton2 time, that controls output2. Here,  $Ton2 \le Ton1$ .

Fig. 3.11. Inductor Voltages and Currents for Output1 and Output2

The inductors have an integral voltage of zero over a period. From figure 3.11.

$$Ton1 * (nVpri1 - Vout1) = (Ts - Ton1) * (-Vout1)$$

$$or, Ton1 * (nVpri1 - Vout1) = (Ts - Ton1) * Vout1$$

$$\frac{Vout1}{Vpri1} = \frac{Ton1}{Ts} * n1$$

Here,  $\frac{Ton1}{Ts} = D1$  which is the duty cycle for the switching signal. Also, |Vpri1| = |Vin| The calculation is same for the second load. So, the transfer functions for the loads are:

$$\frac{Vout1}{Vpri1} = n1 * D1 \tag{3.9}$$

$$\frac{Vout2}{Vpri2} = n2 * D2 \tag{3.10}$$

As,  $Ton2 \le Ton1$ ,  $D2 \le D1$ . The second load is controlled independently, but the maximum duty cycle it can have will be equal to the duty cycle of the first load. It can be seen by comparing equations (3.9) and (3.10) with equations (2.2) and (2.3), the transfer function of the proposed design matches the conventional one.

### 3.11 Feedback Control System

A control system is an interconnection of components forming a system to provide desired system response. The use of a signal, that is proportional to the error between desired and actual response, to control the process results in a closed loop sequence of operations. This is called a feedback system [69]. Most power electronic system rely on feedback control system. Figure 3.12 shows a basic feedback control system for the converter.

While designing the feedback controller to regulate the output voltage, the following objectives are taken into consideration [70]:

- Zero steady state error

- Fast response to changes in the input voltage and the output load

Fig. 3.12. Basic Feedback Control System for the Converter

- Low overshoot

- Low noise susceptibility

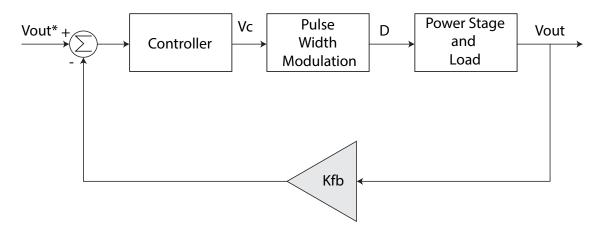

The feedback control system [71] in figure 3.13, the output voltage Vout is measured and compared with a reference value Vout\*. The difference between these two signals is called the error and it acts on the controller.

Fig. 3.13. Feedback Control System for the Converter

The voltage produced by the controller is Vc(t). This control voltage is the input to the pulse-width modulator that produces a switching signal. The average value of that signal is d(t). The duty cycle is D. Linearizing around the steady state operating point, small-signal perturbations are assumed. The equations are shown below:

$$\overline{Vout}(t) = Vout + V\tilde{o}ut(t) \tag{3.11}$$

$$d(t) = D + \tilde{d}(t) \tag{3.12}$$

$$Vc(t) = Vc + \tilde{Vc}(t) \tag{3.13}$$

The average value of the output voltage including the small-signal perturbation would be like the one in equation (3.11). As mentioned earlier, d(t) is the average value. There is no switching frequency component present in Vc(t).

From figure 3.13, the feedback gain is Kfb. The transfer function of the voltage-sensing networks can be represented by this gain. This gain is usually less than unity.

This feedback control system is integrated with the designed converter to regulate the output voltage within the specified tolerance band in order to ensure uninterrupted power supply for the machines.

# 4. RESULTS OBTAINED FROM THE PROPOSED DC-DC CONVERTER

### 4.1 Introduction

Any design that meet the requirements theoretically is needed to be tested to ensure that the design works for real-life situations. The converter designed in the previous chapter was drawn and simulated to guarantee the feasibility of the design.

In this chapter, the results obtained from the simulations are discussed and verified for different conditions. Switching and conduction losses are obtained and calculated for both of the converters. The comparative analyses are also presented in this chapter.

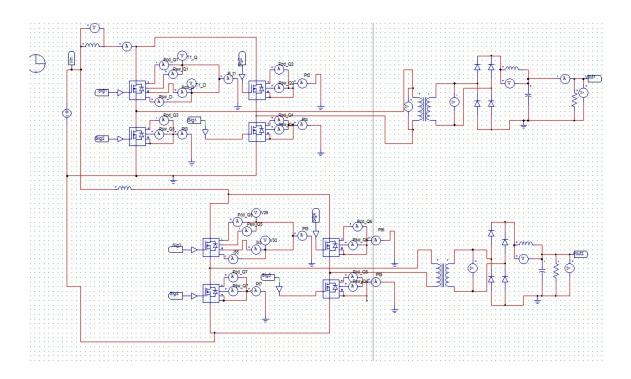

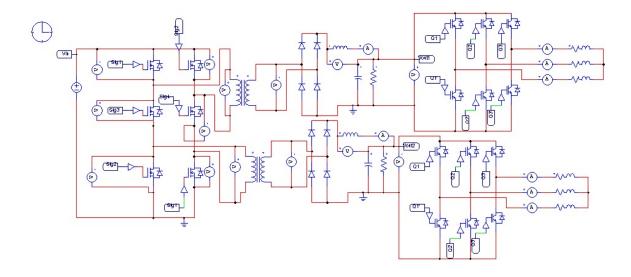

Electronic circuit simulation software package PSIM was used to simulate the designed converter. PSIM has different modules are very useful in power electronic design and can be easily implemented and integrated with other popular platforms, such as TI kits, JMAG, Modelsim, and Simulink [72].

## 4.2 Circuit Diagrams to Simulate Proposed Dc-dc Converter

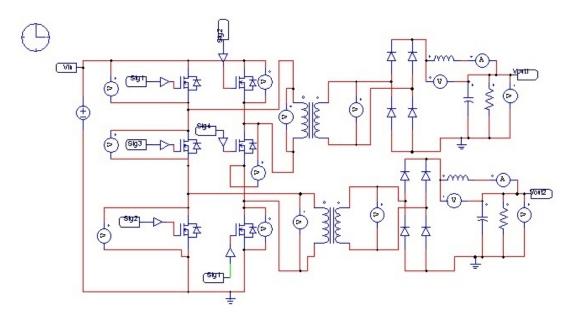

While implementing the design initially, the ideal MOSFETs were used in the schematic. From the menu bar in PSIM, "Elements" was clicked. Then from the drop down menu, Power → Switches → MOSFET was selected to and placed six times in two columns as the switches of the converter. The source in a dc voltage and so Elements → Sources → Voltage → DC was selected as the input dc voltage. The values of the components are given by double clicking of the elements and entering the magnitudes. The other components are selected from the Elements → Power module. From the module, the resistors, capacitors and inductors are placed from "RLC Branches". There is a subsection named

"Transformers" in the "Power" module. The transformers are selected from that subsection. The diodes here are placed from the "Switches" subsection.

After the placement of the elements in their convenient positions, they are connected through wires. The ground was connected at the bottom of the diagram for proper current flow through the circuit. Connecting the gating signals to the diagrams by wires can make the diagram complicated and cumbersome as it contains different logic gates and there are chances of wrong connections and misplaced nodes. For that reason, the gating signal circuitry was placed separately and the labels were used to provide signal inputs in the switches. The switches cannot be connected to the labels through wires or placing close to it. An additional element is required between the switch and the signal. Elements  $\rightarrow$  Other  $\rightarrow$  Switch Controllers  $\rightarrow$  On-Off Controller was selected and placed between all switches and their corresponding signal labels.

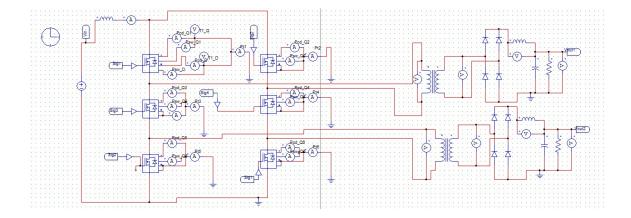

Fig. 4.1. Diagram in PSIM to Simulate the Designed Converter

Figure 4.1 is the diagram drawn on PSIM. For the primary stage of the simulation, ideal MOSFETs were used as switches for simplicity. After successful evaluation of the design, practical switches are employed in stead of the ideal ones.

The MOSFET switches are an active switch with an anti-parallel diode. It is turned on when the gating signal is a logic high and the switch is positively biased (drain-source voltage is positive). Whenever the gating signal is low or the current drops to zero it turns off.

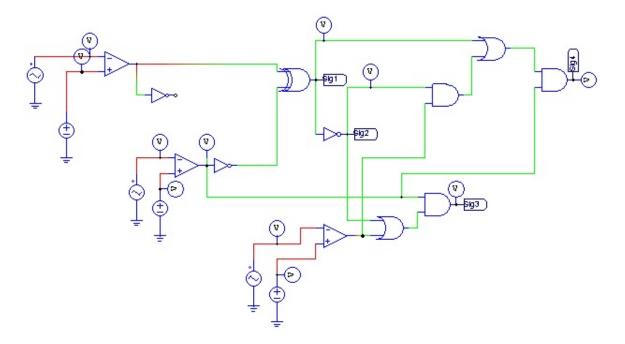

For the gating circuit, the logic gates are selected from Elements  $\rightarrow$  Control  $\rightarrow$  Logic Elements. The Op-Amps are found in the "Other" subsection of the "Power" module.

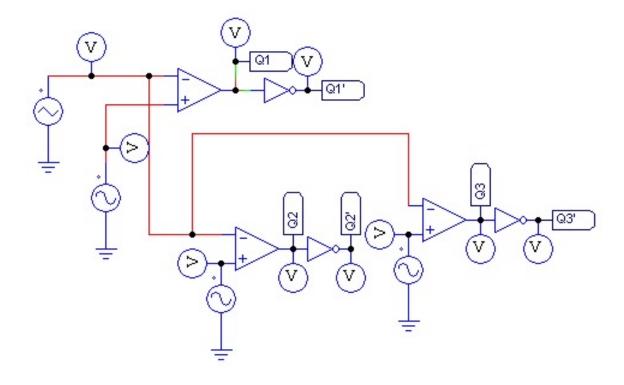

Fig. 4.2. Gating Circuitry to Generate the Switching Signals

Figure 4.2 is the gating circuitry in PSIM that generate the switching signals. Four signals were generated here as signals Sig1 and Sig2 were used as the switching signals for the sixth and fifth switches respectively apart from the first and second switches. The labels are placed in the parts where the desired signals are generated.

As mentioned before, while connecting these labels as the gating signals to the switches, the "On-Off Controllers" are required. On-off switch controller works as the interface between the control gating signals and the power switches. The switches are controlled by the gating signal which are the input logic signal generated from the control circuit is passed to the power circuit [73]. The "On-Off Controllers" are placed between the signal labels and the power switches.

### 4.3 Results From Simulation

After all the circuits are completed, from the menu bar "Simulation" is clicked and from the drop down menu, "Simulation Control" is selected. Then the cursor changes into a clock symbol. This clock is placed at a side on the schematic. The properties like time step, total time etc. can be changed by double clicking on the symbol.

Table 4.1. Parameters of Simulation Control

| Parameters | Value  |

|------------|--------|

| Time step  | 4E-006 |

| Total time | 4      |

| Print time | 1      |

| Print step | 1      |

The parameters that are included in "Simulation Control" are shown in table 4.1. Other parameters are left as it was. Then the simulation is run by selecting "Run Simulation" from "Simulation" menu. After the simulation is completed, "Run SIMVIEW" is selected from the same menu to launch the waveform display program. Then by selecting the waveforms of the previously placed probes, the waveforms are displayed.

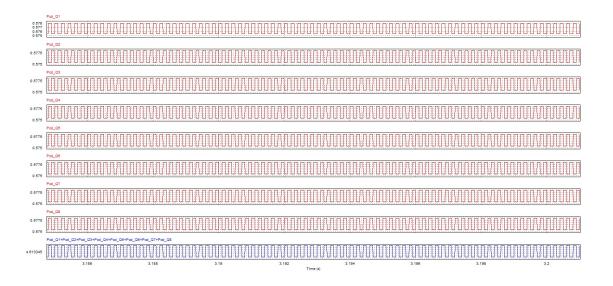

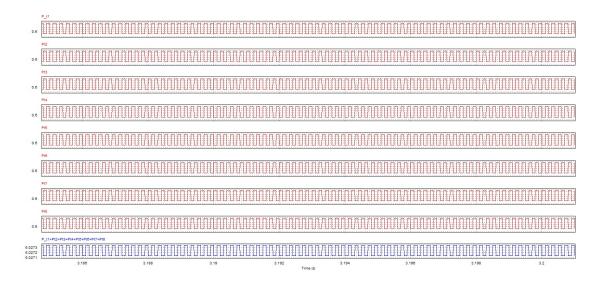

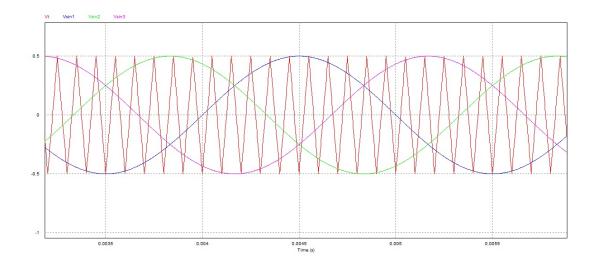

The required switching signals found from the simulation are shown in figure 4.3. Note that these switching signals are similar to the expected switching signals.

Fig. 4.3. Four Switching Signals Generated to Control the Voltage at Primary Side

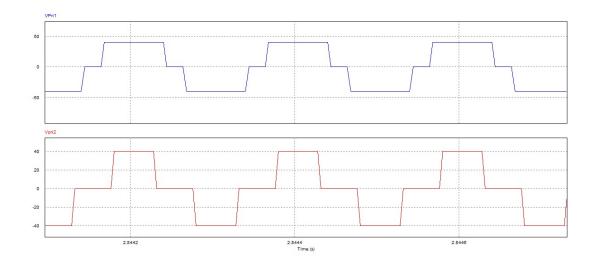

Load-1 was given a reference voltage of 0.8 magnitude and Load-2 was given a reference voltage of 0.5 magnitude during this simulation. So the duty cycle for load-1 (the upper load) is 0.8 and the duty cycle for load-2 (the lower load) is 0.5 as the magnitude of the triangular voltage was 1.

Figure 4.4 shows the voltages at primary sides according to the given duty cycles.

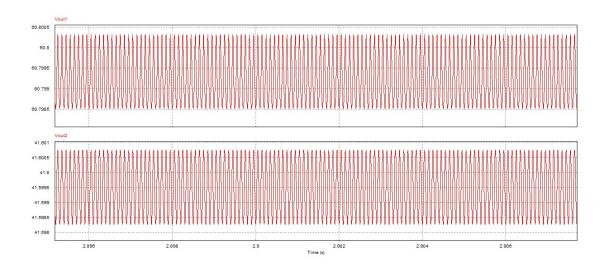

For this simulation, the input voltage is set as 40 volts. The turns ratios of the transformers are given as 1:2 for both of the loads. The output voltages of both of the loads found from this simulation are shown in figure 4.5. Apparently, the output voltage of load-1 is higher than the output voltage of load-2.

## 4.4 Calculations

From the transfer function of the converter, the output voltages can be calculated. Equation (3.9) in chapter 3 of this thesis gives the transfer function of load-1 of the converter and equation (3.10) gives the transfer function of load-1 of the converter.

Fig. 4.4. Primary Side Voltages [Upper one with 0.8 duty cycle and lower one with 0.5 duty cycle]

Fig. 4.5. Output Voltages of Load-1 and Load-2